# CAPACITANCE-VOLTAGE SPECTROSCOPY IN METAL – TANTALUM PENTOXIDE (Ta<sub>2</sub>O<sub>5</sub>) – SILICON MOS CAPACITORS

A Thesis Submitted to the Graduate School of Engineering and Science of İzmir Institute of Technology in Partial Fulfillment of Requirements for the Degree of

**MASTER OF SCIENCE**

in Physics

by Pınar ÖZDAĞ

> July 2005 İZMİR

# **ACKNOWLEDGEMENTS**

I would like to thank to my advisor, Assoc. Prof. Mehmet GÜNEŞ for his help and support during my master of science thesis.

I am also thankfull to Prof. Elena Atanassova from Bulgarian Academy of Sciences for supplying the samples that are used in this study.

I am grateful to İzmir Institute of Technology (IYTE) for giving me a full time assistantship during my thesis.

I would like to thank to all of my friends at İzmir Institute of Technology, and especially to Elif for always being next to me.

Finally, I am gratefull to my family and husband Melih for their help, support and love.

#### **ABSTRACT**

The electronic properties of Al-Ta<sub>2</sub>O<sub>5</sub>-Si MOS capacitors with oxide layers prepared by RF magnetron sputtering with or without a prior nitridation process in N<sub>2</sub>O or NH<sub>3</sub> gas environments at temperature ranges between 700 °C to 850 °C were investigated using Capacitance-Voltage (C-V) Spectroscopy to determine the quality of oxide layer and oxide-silicon interface. The theoretical ideal capacitance-voltage calculations were compared with the experimental capacitance-voltage results in order to evaluate effective oxide charges,  $Q_{\rm eff}$ , present inside Ta<sub>2</sub>O<sub>5</sub> insulating layer and density of interface trap states, Dit, present at the Ta<sub>2</sub>O<sub>5</sub>-Si interface. In addition, dielectric constant, doping concentration, flat band voltage values were determined by using the experimental data. Finally, the effects of deposition conditions on Ta<sub>2</sub>O<sub>5</sub> MOS capacitors were compared by using a reference sample of a MOS capacitor with native oxide SiO<sub>2</sub>.

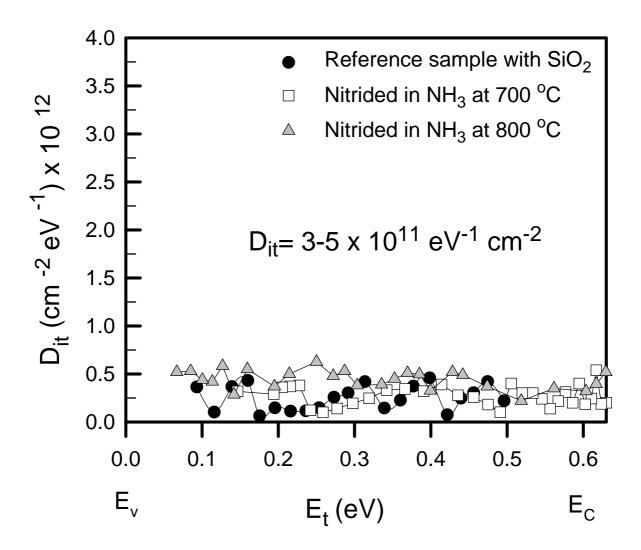

It has been found that dielectric constant value up to 12 have been reached for  $Ta_2O_5$  insulating layers which increases the capacitance value several times than that of MOS capacitor with native oxide  $SiO_2$ . The density of interface trap states,  $D_{it}$ , for unnitrided  $Ta_2O_5$  MOS capacitors, values around  $1.6x10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> have been detected which is much higher than that of MOS capacitor with native oxide  $SiO_2$ . However, prior nitridation process enhances the interface properties and  $D_{it}$  values down to  $2-5x10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> have been reached for the nitrided samples which is in the limits for MOS capacitors with high quality insulating layers. In addition, the effective oxide charges,  $Q_{eff}$ , for unnitrided samples, values as high as  $3x10^{12}$  cm<sup>-2</sup> were detected. Even though nitridation process enhances interface properties, the effective oxide charges are found to be higher for nitrided samples. Best electrical and interface properties are obtained by nitridation process at 800 °C in  $N_2O$  and  $NH_3$ . It can be inferred that samples nitrided in  $N_2O$  gas at 800 °C improves the dielectric constant above the level of  $SiO_2$  and decreases both  $Q_{eff}$  and  $D_{it}$  levels to that of native oxide  $SiO_2$ .

These results show that a prior nitridation of p-silicon surface is a promising approach to improve both oxide and interface properties of Al-Ta<sub>2</sub>O<sub>5</sub>-Si MOS devices. However, further investigation is necessary to understand the nature of these oxide charges and interface properties of MOS devices with high dielectric constant oxide layers before integration into large scale fabrication.

# ÖZET

RF (yüksek frekans) magnetron püskürtme tekniğiyle hazırlanmış, Al-Ta<sub>2</sub>O<sub>5</sub>-Si metal-oksit-yarıiletken (MOS) sığaların bir kısmı oksit tabakasının büyütülmesinden önce N<sub>2</sub>O ve NH<sub>3</sub> gaz ortamlarında 700-850 °C alttaş sıcaklık aralığında nitrürleme işlemine maruz bırakılmış, ve nitrürlenmiş ile nitrürlenmemiş örneklerin elektriksel özellikleri, oksit tabakasının ve oksit-yarıiletken ara yüzeyinin kalitesi Sığa-Gerilim metoduyla incelenmiştir. Teorik ideal kapasite-gerilim hesaplamaları deneysel kapasite-gerilim ölçümleriyle karşılaştırılmış ve Ta<sub>2</sub>O<sub>5</sub> oksit tabakası içindeki etkin oksit yük yoğunluğu, Q<sub>eff</sub>, ve Ta<sub>2</sub>O<sub>5</sub>-Si ara yüzeyindeki tuzak yoğunluğu, D<sub>it</sub>, hesaplanmıştır. Bunun yanı sıra deneysel veriler kullanılarak, dielektrik sabiti, katkılama yoğunluğu, düz bant gerilim değerleri bulunmuştur. Son olarak, oksit büyütme koşullarının Ta<sub>2</sub>O<sub>5</sub> MOS sığalar üzerindeki etkisi referans örneği olan SiO<sub>2</sub> MOS sığayla karşılaştırılmıştır.

Sonuç olarak, Ta<sub>2</sub>O<sub>5</sub> MOS sığalar için 12 ye varan dielektrik sabitleri elde edilmiştir ki bu değer sığa değerini SiO<sub>2</sub> MOS sığanın sığa değerinden bir kaç kat yukarıya çıkarmıştır. Ara yüzey tuzak yoğunluğu, D<sub>it</sub>, nitrürlenmemiş örnekler için 1.6x10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup> civarında bulunmuştur. Ancak bu değer SiO<sub>2</sub> MOS sığanın ara yüzey tuzak yoğunluğuyla karşılaştırıldığında yaklaşık olarak beş katlık bir artış gözlemlenmiştir. Öte yandan nitrürleme işlemi ara yüzeyin kalitesini arttırmış ve nitrürlenmiş örnekler için D<sub>it</sub> değeri 2-5x10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> civarına düşürülmüştür. Etkin oksit yükleri açısından, Q<sub>eff</sub>, nitrürlenmemiş örnekler için 3x10<sup>12</sup> cm<sup>-2</sup> ye kadar artan değerler hesaplanmıştır. Nitrürleme işlemi ara yüzey kalitesini arttırsa bile, Q<sub>eff</sub> değerleri SiO<sub>2</sub> MOS sığayla karşılaştırıldığında hala yüksek olduğu gözlemlenmiştir. En iyi elektriksel ve ara yüzey özellikleri 800 °C'de yapılan nitrürleme işlemi sonuçunda elde edilmiştir. Sonuç olarak, N<sub>2</sub>O gaz ortamında 800 °C'de yapılan nitürleme işlemi dielektrik sabitini arttırmış ve etkin oksit yük yoğunluğu, Q<sub>eff</sub>, ve ara yüzey tuzak yoğunluğu, D<sub>it</sub>, değerlerini SiO<sub>2</sub> MOS sığanın değerlerine kadar düşürmüştür.

Bu sonuçlar gösteriyor ki, nitürleme işlemi Al-Ta<sub>2</sub>O<sub>5</sub>-Si MOS sığaların oksit ve oksit-yarıiletken ara yüzey özelliklerini geliştirmede umut vaad eden bir yaklaşımdır. Ancak, büyük ölçeklerde fabrikasyon işlemine geçmeden önce yüksek dielektik sabitine sahip MOS sığalardaki oksit yüklerinin ve ara yüzey tuzak yoğunluklarının incelenmesi ve iyileştirilmesi gerekmektedir.

# TABLE OF CONTENTS

| LIST OF FI | IGURES                                                                                                    | viii |

|------------|-----------------------------------------------------------------------------------------------------------|------|

| LIST OF TA | ABLES                                                                                                     | xiii |

| CHAPTER    | 1. INTRODUCTION                                                                                           | 1    |

|            | 1.1. Thesis Objectives                                                                                    | 8    |

| CHAPTER    | 2. EXPERIMENTAL                                                                                           | 10   |

|            | 2.1. Sample Preparation                                                                                   | 10   |

|            | 2.2. Characterization Techniques.                                                                         | 13   |

|            | 2.2.1. Capacitance-Voltage (C-V) Spectroscopy                                                             | 13   |

| CHAPTER    | 3. PHYSICS OF MOS DEVICES AND ANALYSIS                                                                    | 19   |

|            | 3.1.Ideal Metal-Oxide-Semiconductor (MOS) Energy Band Diagrams                                            | 19   |

|            | 3.2. Theoretical Capacitance of Ideal MOS Structure                                                       | 24   |

|            | 3.3. Non-ideal Effects                                                                                    | 31   |

|            | 3.4. Analysis of Non-ideal Effects                                                                        | 33   |

|            | 3.4.1.Calculation of Flat Band Voltage and Doping Concentration                                           | 33   |

|            | 3.4.2. Calculation of Effective Oxide Charges                                                             | 36   |

|            | 3.4.3. Derivation of Density of Interface Trap States (Dit)                                               | 36   |

|            | 3.4.3.1. High Frequency Capacitance-Voltage Method (Terman's                                              |      |

|            | Method)                                                                                                   | 36   |

|            | 3.4.3.2.Combined High-Low Frequency Capacitance Method                                                    |      |

|            | (Simultaneous C-V Method)                                                                                 | 39   |

| CHAPTER    | 4. EXPERIMENTAL RESULTS                                                                                   | 41   |

|            | 4.1.Introduction                                                                                          | 41   |

|            | 4.2.Results of Al-SiO <sub>2</sub> -Si MOS Capacitors (Reference Sample)                                  | 41   |

|            | 4.3.Results of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>2</sub> )-Si MOS Capacitors Set 1: The Effect |      |

|            | of Oxide Thickness                                                                                        | 50   |

| 4.4.Results of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS Capacitors Set 2: The |    |

|-------------------------------------------------------------------------------------------------------------------|----|

| Effect of Nitridation Process                                                                                     | 60 |

| 4.4.1.Nitridation of Silicon Surface by N <sub>2</sub> O Gas                                                      | 60 |

| 4.4.2.Nitridation of Silicon Surface by NH <sub>3</sub> Gas                                                       | 72 |

| 4.5.Conclusions                                                                                                   | 86 |

| CHAPTER 5. DISCUSSIONS AND CONCLUSIONS                                                                            | 87 |

| REFERENCES                                                                                                        | 92 |

# **LIST OF FIGURES**

| <b>Figure</b> | <u> 1</u>                                                                                     | Page |

|---------------|-----------------------------------------------------------------------------------------------|------|

| Figure 2.1    | Schematic view of MOS structures that are used in this study                                  | 10   |

| Figure 2.2    | Simultaneous Capacitance-Voltage (C-V) Setup                                                  | 13   |

| Figure 2.3    | Model 82 Main Menu                                                                            | 15   |

| Figure 2.4    | Characterization of device Parameters Menu                                                    | 15   |

| Figure 2.5    | Measurement parameter List Menu                                                               | 16   |

| Figure 2.6    | High and Low frequency C-V graphics of a MOS device                                           | 16   |

| Figure 2.7    | Device Measurement and Analysis Menu                                                          | 17   |

| Figure 2.8    | Sweep Data Analysis Menu                                                                      | 18   |

| Figure 3.1    | Ideal MOS Structure with applied gate voltage V <sub>G</sub>                                  | 19   |

| Figure 3.2    | Energy-Band diagram of ideal MOS structure in thermal                                         |      |

|               | equilibrium constructed from a p-type semiconductor substrate                                 | 20   |

| Figure 3.3    | Cross-section and energy band diagram of MOS capacitor in                                     |      |

|               | accumulation region                                                                           | 22   |

| Figure 3.4    | Cross-section and energy band diagram of MOS capacitor in                                     |      |

|               | depletion region                                                                              | 22   |

| Figure 3.5    | Cross-section and energy band diagram of MOS capacitor in                                     |      |

|               | inversion region                                                                              | 23   |

| Figure 3.6    | Capacitance equivalent circuit of a MOS capacitor, where total                                |      |

|               | capacitance is a series combination of $C_{ox}$ and $C_{Si}$                                  | 25   |

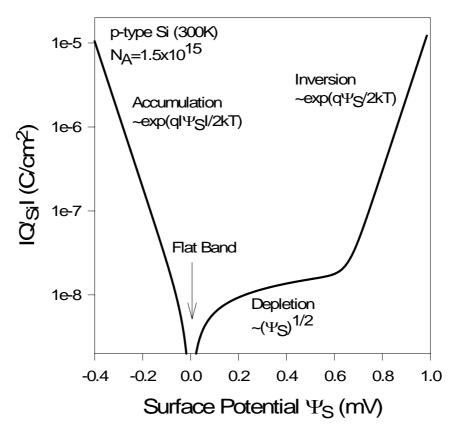

| Figure 3.7    | Variation of the magnitude of the charge density Q'si in the                                  |      |

|               | semiconductor as a function of the surface potential $\psi_{\scriptscriptstyle S}$ for p-type |      |

|               | Si with $N_A=1.5 \times 10^{15}$ cm <sup>-3</sup> at room T.                                  | 28   |

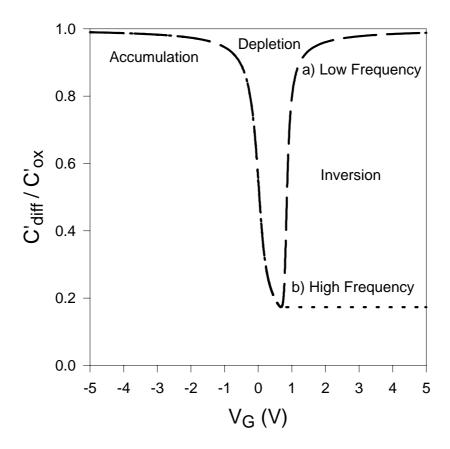

| Figure 3.8    | Theoretical ideal MOS Capacitance-Voltage curves for a) low                                   |      |

|               | frequency, and b) high frequency                                                              | 31   |

| Figure 3.9    | Terminology for the names and location of charges in a non-ideal                              |      |

|               | MOS structure                                                                                 | 32   |

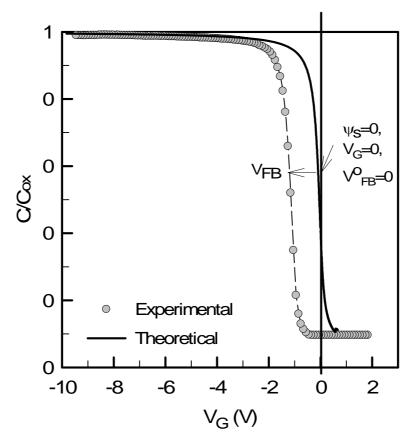

| Figure 3.10   | Theoretical (ideal) and experimental high frequency capacitance-                              |      |

|               | voltage curves of a MOS capacitor with a p-type silicon substrate                             | 34   |

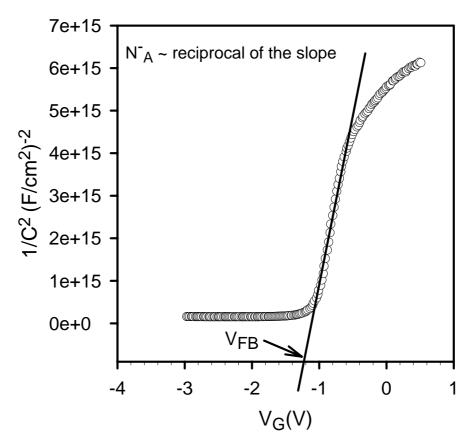

| Figure 3.11   | 1/C <sup>2</sup> versus gate voltage V <sub>G</sub> graph of a MOS capacitor                  | 35   |

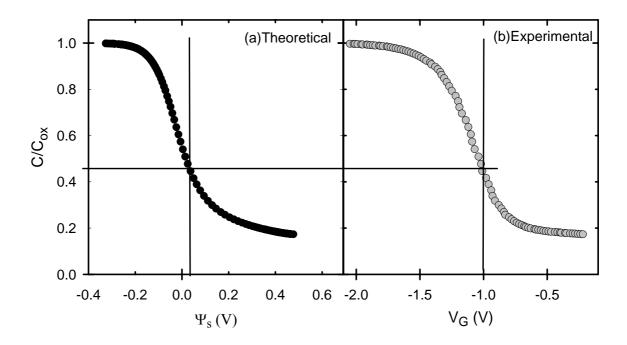

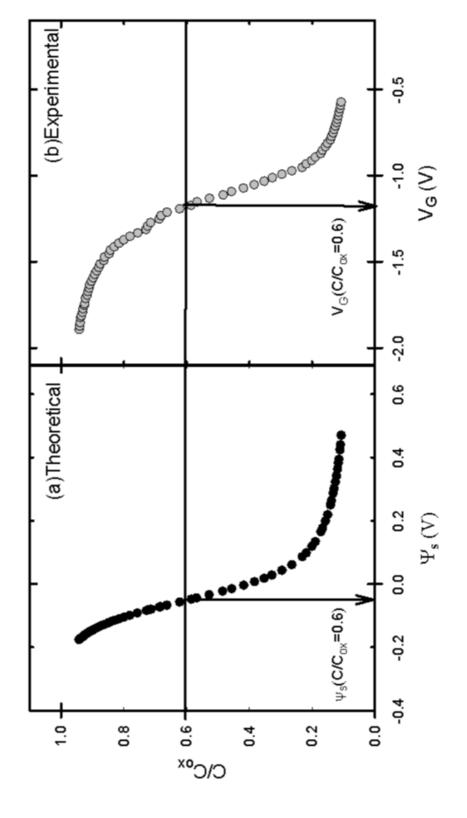

| Figure 3.12 | A theoretical C versus $\psi_s$ plot compared with a hypothetical C                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------|

|             | versus V <sub>G</sub> plot for a MOS capacitor                                                                  |

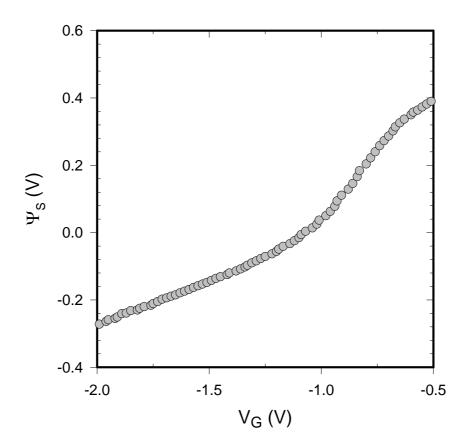

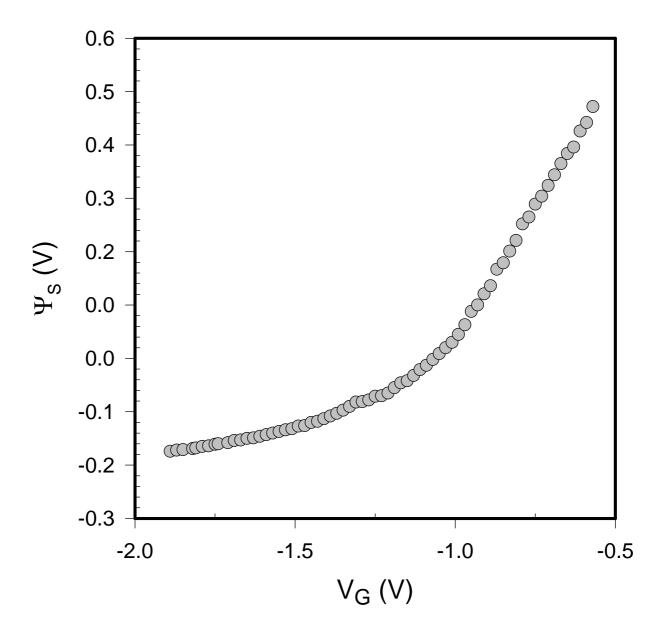

| Figure 3.13 | The surface potential $\psi_S$ versus gate voltage $V_G$ obtained from the                                      |

|             | theoretical and experimental high frequency C/Cox curves of a                                                   |

|             | MOS capacitor shown in Figure 3.12.                                                                             |

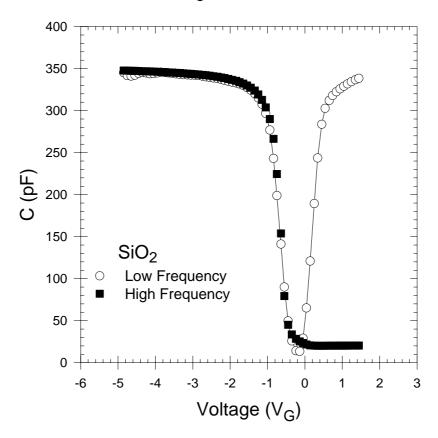

| Figure 3.14 | Measured C <sub>HF</sub> and C <sub>LF</sub> versus V <sub>G</sub> curves for native SiO <sub>2</sub> sample40  |

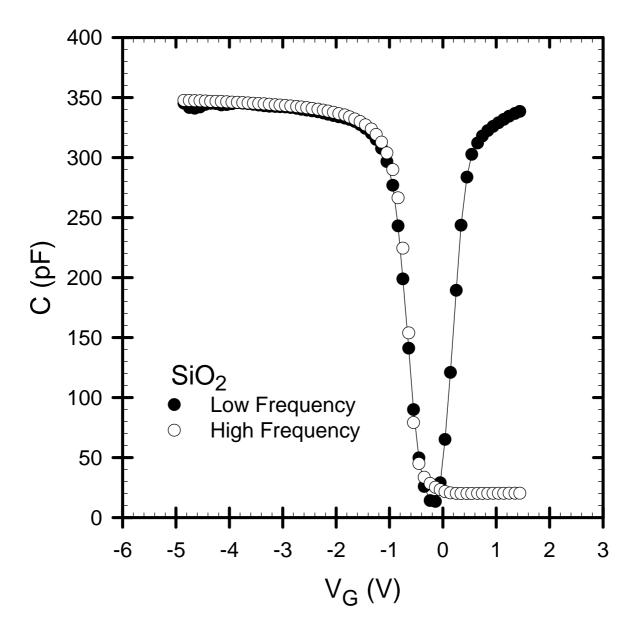

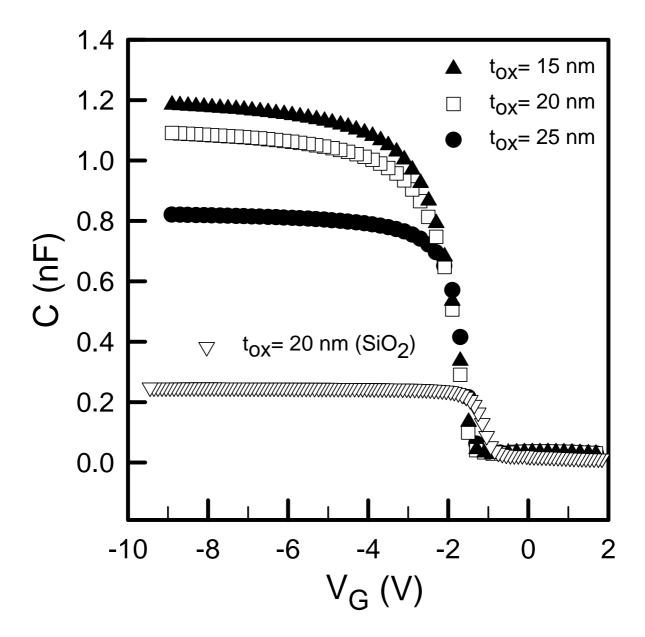

| Figure 4.1  | Low and High frequency (1 MHz) capacitance-voltage curves of Al-                                                |

|             | SiO <sub>2</sub> -Si MOS capacitors                                                                             |

| Figure 4.2  | Experimental high frequency 1/C² versus gate voltage V <sub>G</sub> graph of                                    |

|             | the Al-SiO2-Si reference sample for the determination of doping                                                 |

|             | concentration and flat band voltage                                                                             |

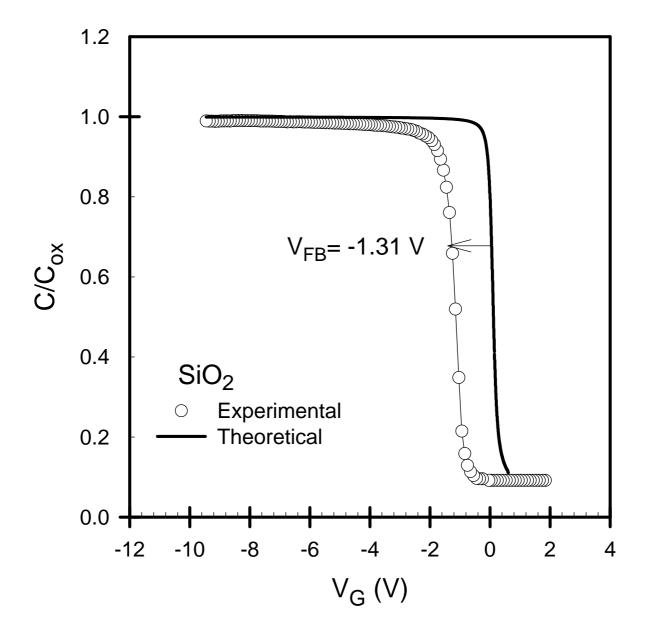

| Figure 4.3  | Theoretical (ideal) and experimental high frequency (1 MHz)                                                     |

|             | Capacitance-Voltage Curves of an Al-SiO <sub>2</sub> -Si MOS capacitor45                                        |

| Figure 4.4  | (a) Theoretical normalized capacitance versus surface potential and                                             |

|             | (b) experimental normalized capacitance versus gate voltage graphs                                              |

|             | for Al-SiO <sub>2</sub> -Si MOS capacitor46                                                                     |

| Figure 4.5  | Surface Potential $\psi_S$ versus gate voltage $V_G$ graph of an Al-SiO <sub>2</sub> -Si                        |

|             | MOS capacitor obtained from the theoretical and experimental high                                               |

|             | frequency C/C <sub>ox</sub> curves                                                                              |

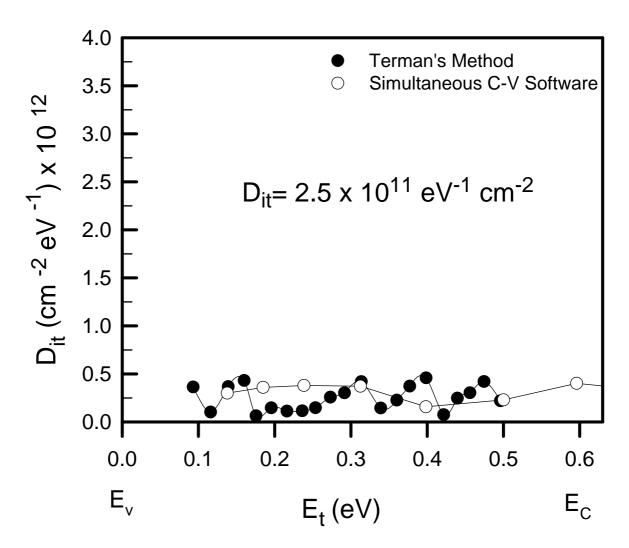

| Figure 4.6  | Density of Interface trap states as a function of energy in the                                                 |

|             | bandgap of c-Si for Al-SiO <sub>2</sub> -Si MOS capacitor calculated both by                                    |

|             | Terman's method and by simultaneous C-V software48                                                              |

| Figure 4.7  | High frequency capacitance versus gate voltage characteristics of                                               |

|             | Al-Ta <sub>2</sub> O <sub>5</sub> -Si MOS capacitors with different oxide thicknesses and                       |

|             | that of the reference MOS sample                                                                                |

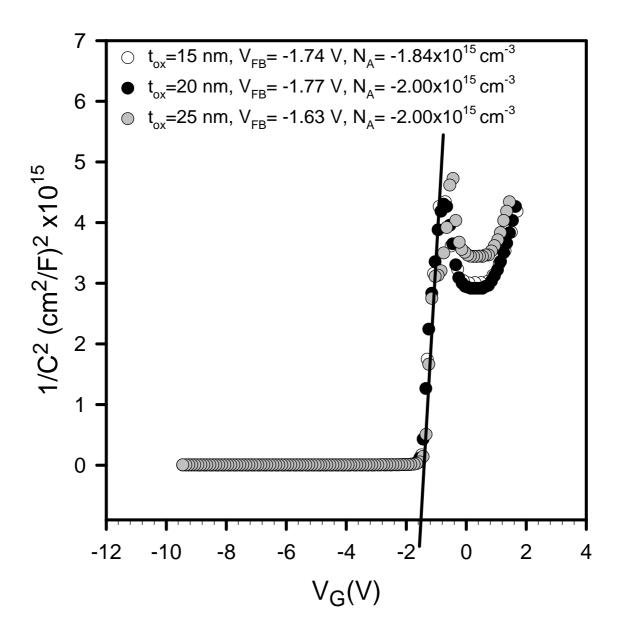

| Figure 4.8  | Experimental 1/C <sup>2</sup> versus gate voltage V <sub>G</sub> graph of Al-Ta <sub>2</sub> O <sub>5</sub> -Si |

|             | MOS capacitors for the determination of doping concentration and                                                |

|             | flat band voltages for oxide thicknesses 15 nm, 20 nm and 25 nm52                                               |

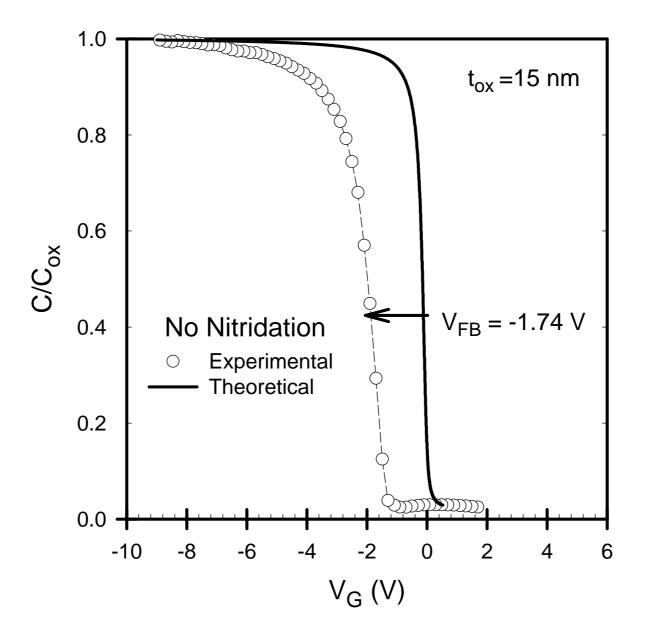

| Figure 4.9  | Theoretical and experimental high frequency normalized                                                          |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -Si MOS capacitor with 15                       |

|             | nm Ta <sub>2</sub> O <sub>5</sub> insulating layer54                                                            |

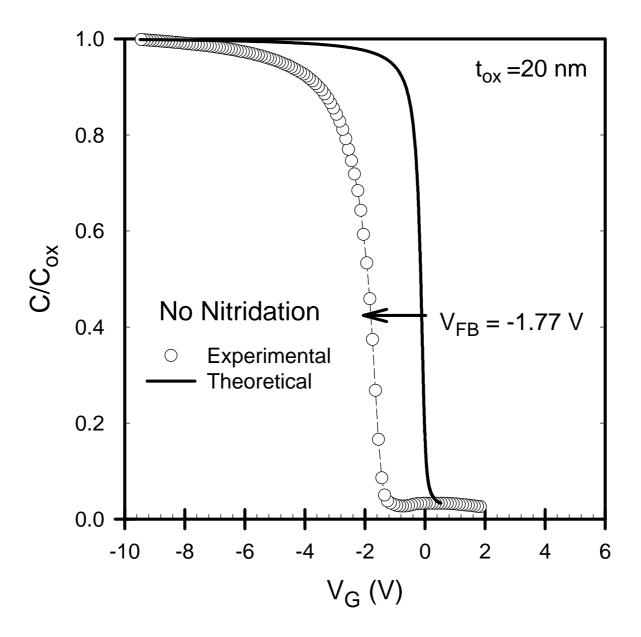

| Figure 4.10 | Theoretical and experimental high frequency normalized                                                                |     |

|-------------|-----------------------------------------------------------------------------------------------------------------------|-----|

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -Si MOS capacitor with 20                             |     |

|             | nm Ta <sub>2</sub> O <sub>5</sub> insulating layer                                                                    | .55 |

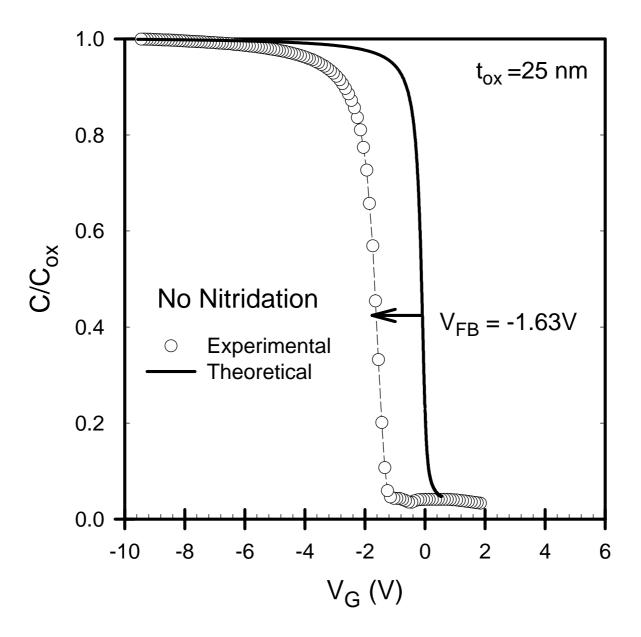

| Figure 4.11 | Theoretical and experimental high frequency normalized                                                                |     |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -Si MOS capacitor with 25                             |     |

|             | nm Ta <sub>2</sub> O <sub>5</sub> insulating layer                                                                    | .56 |

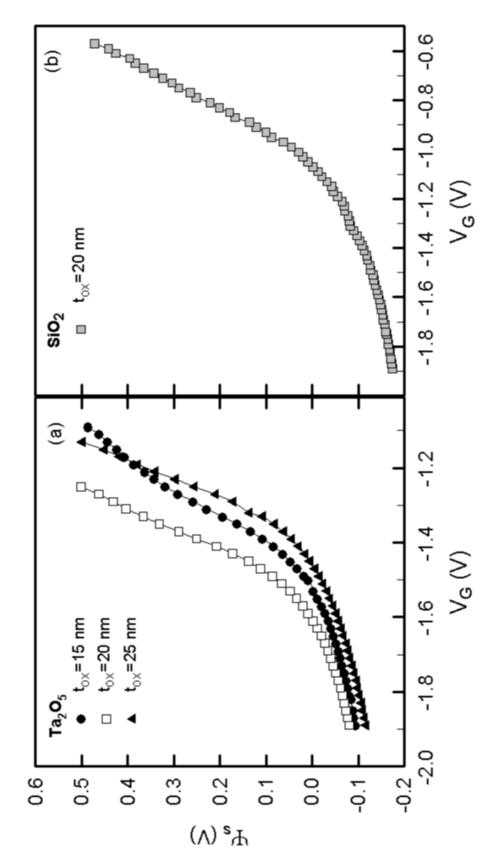

| Figure 4.12 | Surface Potential versus gate voltage V <sub>G</sub> curves for MOS capacitors                                        |     |

|             | with a) $Ta_2O_5$ with $t_{ox}$ =15 nm, 20 nm, and 25 nm and b)SiO <sub>2</sub> with                                  |     |

|             | t <sub>ox</sub> =20 nm                                                                                                | .58 |

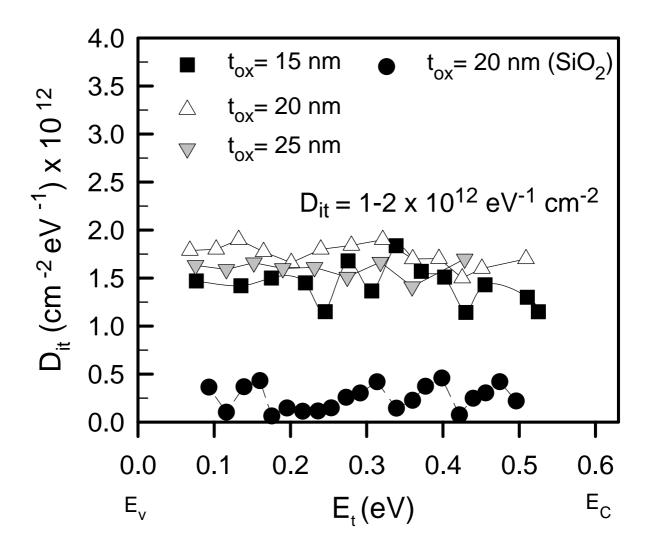

| Figure 4.13 | Density of interface trap states as a function of energy in the                                                       |     |

|             | bandgap of c-Si for MOS capacitors with Ta <sub>2</sub> O <sub>5</sub> insulating layer of                            |     |

|             | different oxide thicknesses and that of the reference sample with                                                     |     |

|             | native oxide SiO <sub>2</sub>                                                                                         | .59 |

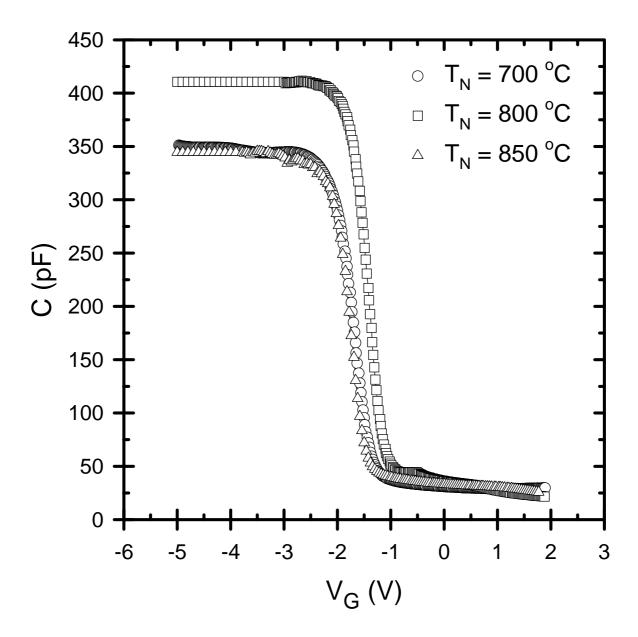

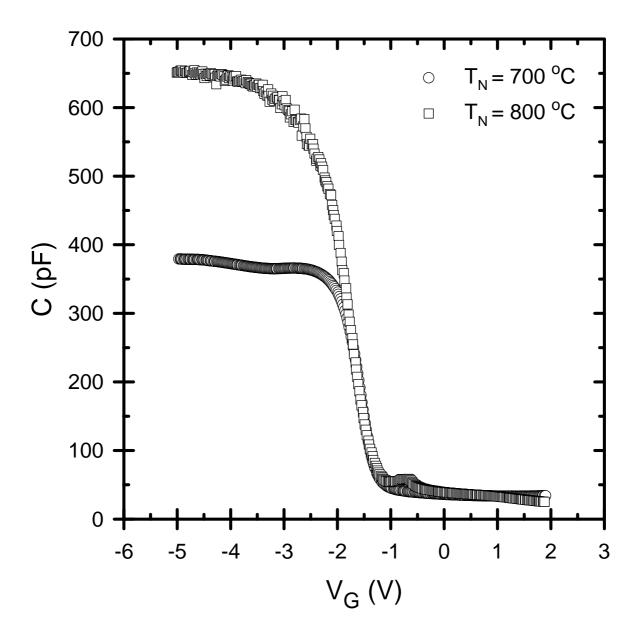

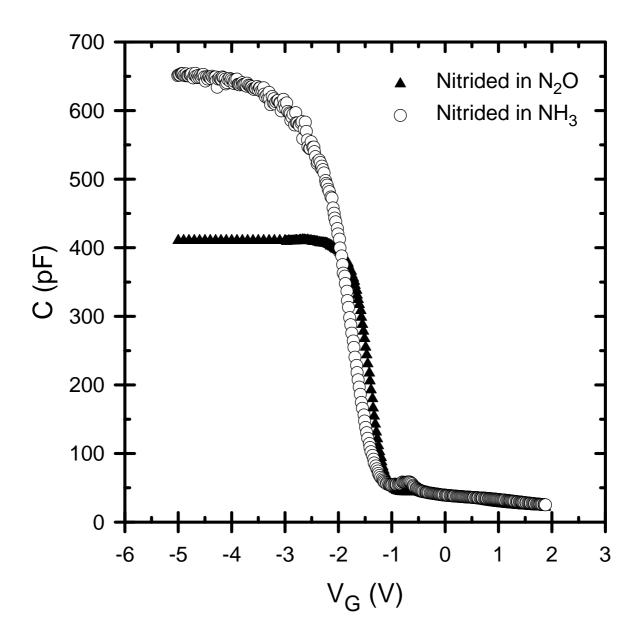

| Figure 4.14 | High frequency capacitance versus gate voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -                          |     |

|             | (SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors for nitridation temperatures of 700°C,                           |     |

|             | 800°C, and 850°C in N <sub>2</sub> O gas environment.                                                                 | .61 |

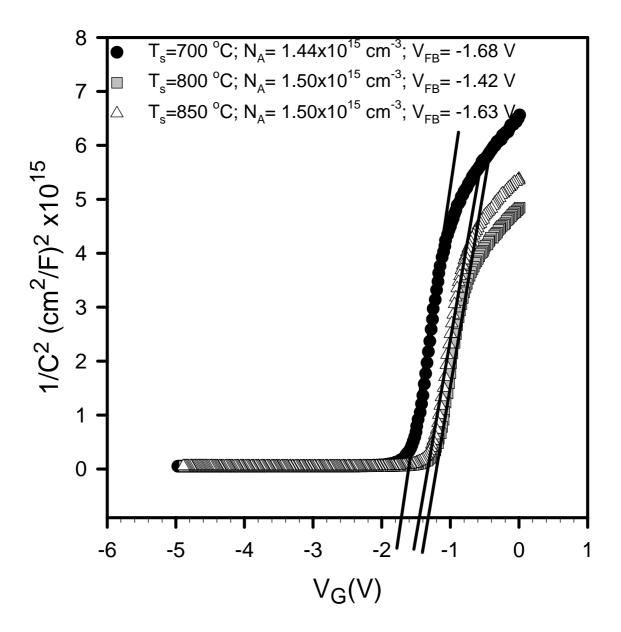

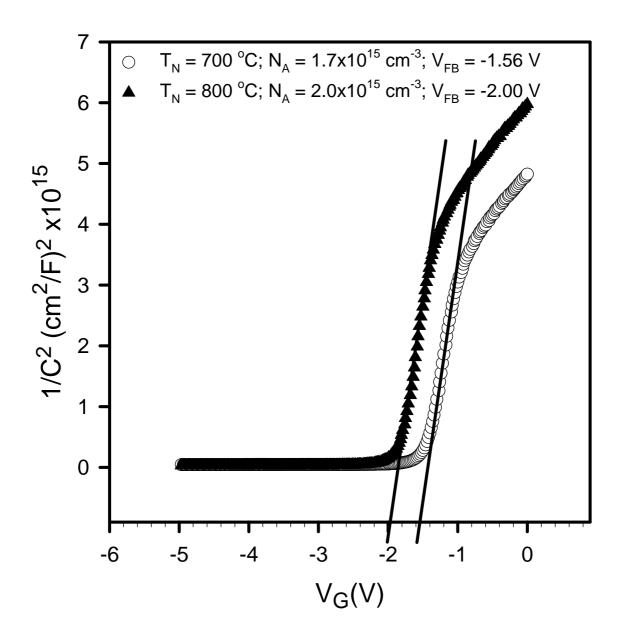

| Figure 4.15 | Experimental 1/C² versus gate voltage V <sub>G</sub> graph of Al-Ta <sub>2</sub> O <sub>5</sub> -                     |     |

|             | (SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors for nitridation processes in N <sub>2</sub> O at                 |     |

|             | 700°C, 800°C, and 850°C.                                                                                              | .63 |

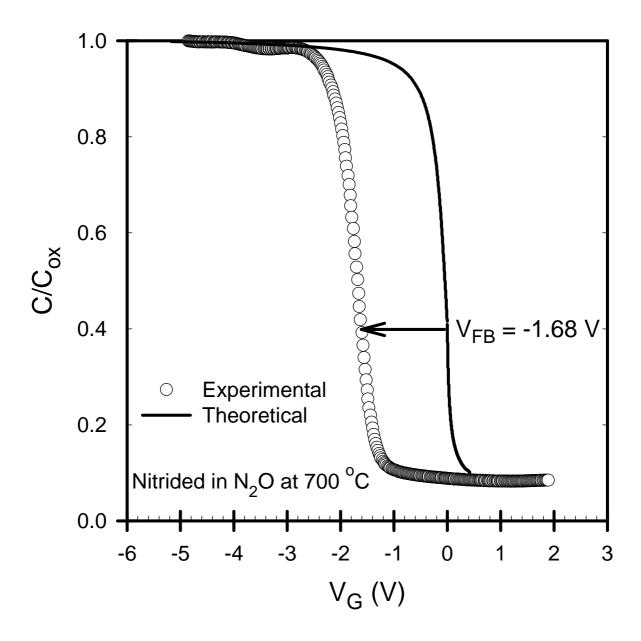

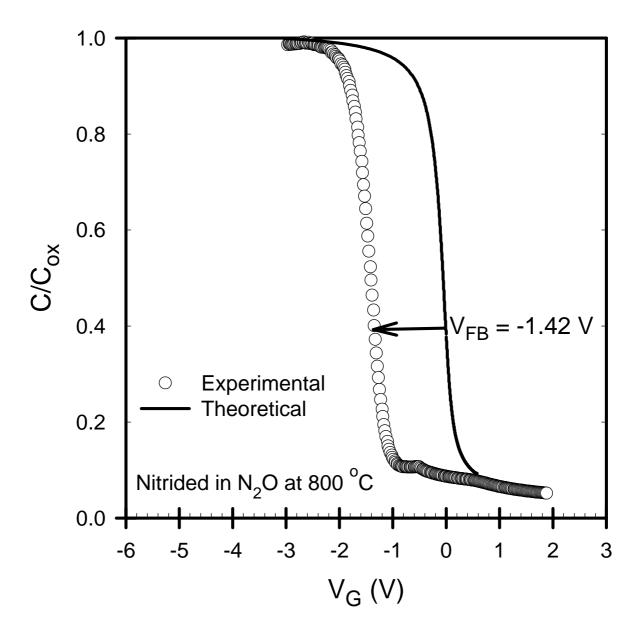

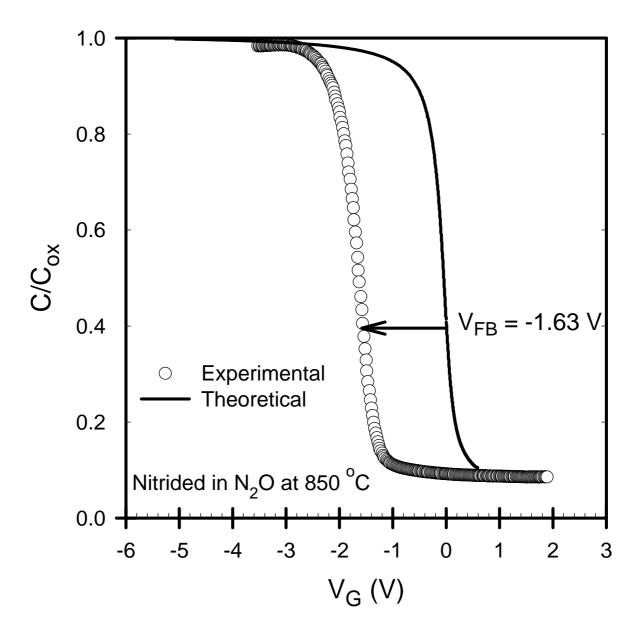

| Figure 4.16 | Theoretical and experimental high frequency normalized                                                                |     |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitor  |     |

|             | prepared after nitridation process in N <sub>2</sub> O at 700°C.                                                      | .64 |

| Figure 4.17 | Theoretical and experimental high frequency normalized                                                                |     |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitor  |     |

|             | prepared after nitridation process in N <sub>2</sub> O at 800°C.                                                      | .65 |

| Figure 4.18 | Theoretical and experimental high frequency normalized                                                                |     |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitor  |     |

|             | prepared after nitridation process in N <sub>2</sub> O at 850°C.                                                      | .66 |

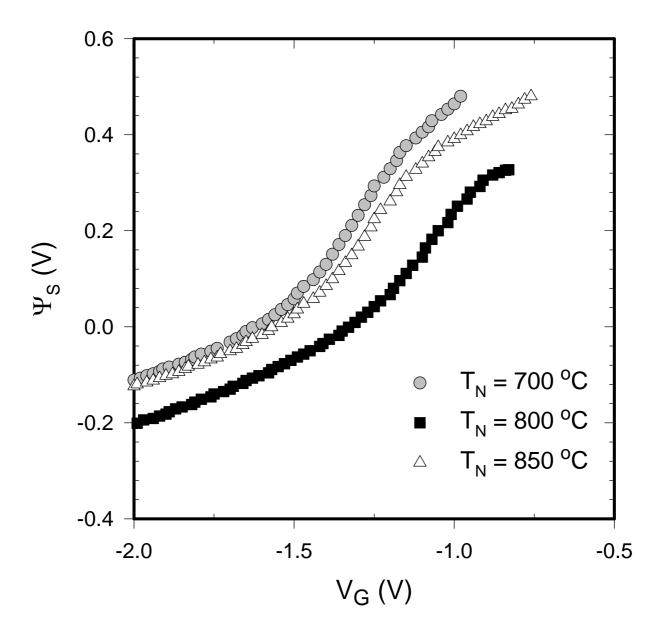

| Figure 4.19 | Surface Potential $\psi_S$ versus gate voltage $V_G$ curves of Al-Ta <sub>2</sub> O <sub>5</sub> -                    |     |

|             | (SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared with a prior nitridation                                |     |

|             | process in N <sub>2</sub> O at 700°C, 800°C, and 850°C                                                                | .69 |

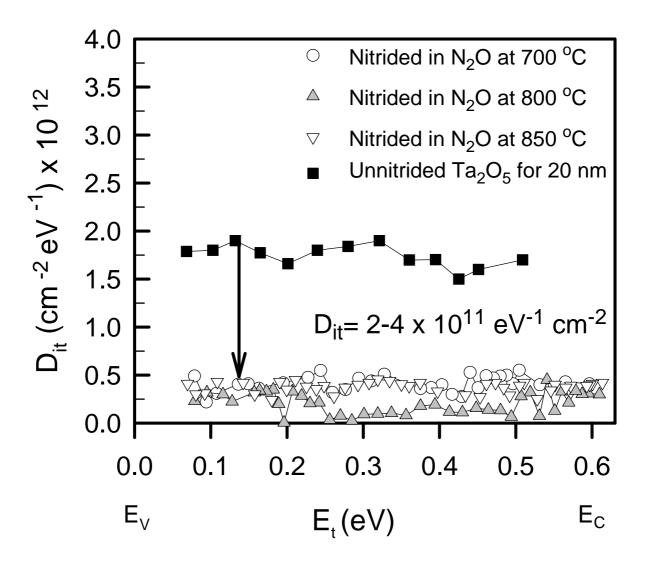

| Figure 4.20 | Density of Interface trap states as a function of energy in the band                                                  |     |

|             | gap of c-Si for Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared with |     |

|             | prior nitridation process in N <sub>2</sub> O at temperatures 700°C, 800°C, and                                       |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------|----|

|             | 850°C and that of unnitrided Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>2</sub> )-Si MOS capacitor                  |    |

|             | with 20 nm thick Ta <sub>2</sub> O <sub>5</sub> layer                                                                 | 0  |

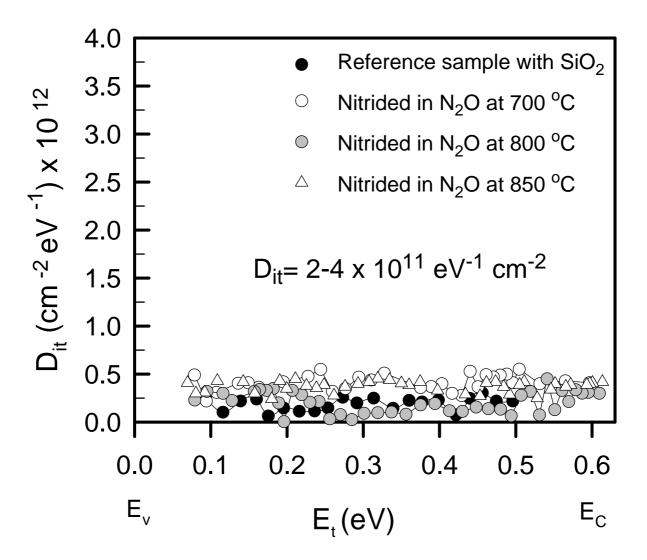

| Figure 4.21 | Density of Interface trap states as a function of energy in the band                                                  |    |

|             | gap of c-Si for Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared with |    |

|             | prior nitridation process in N <sub>2</sub> O at temperatures 700°C, 800°C, and                                       |    |

|             | 850°C and that of reference MOS sample with native SiO <sub>2</sub> layer7                                            | ′1 |

| Figure 4.22 | Experimental high frequency ( 1 MHz) capacitance versus gate                                                          |    |

|             | voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared    |    |

|             | after a nitridation process in NH <sub>3</sub> gas at 700°C and 800°C7                                                | 3  |

| Figure 4.23 | Experimental 1/C <sup>2</sup> versus gate voltage V <sub>G</sub> graph of Al-Ta <sub>2</sub> O <sub>5</sub> -         |    |

|             | (SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared after nitridation process in                            |    |

|             | NH <sub>3</sub> at 700°C and 800°C                                                                                    | 4  |

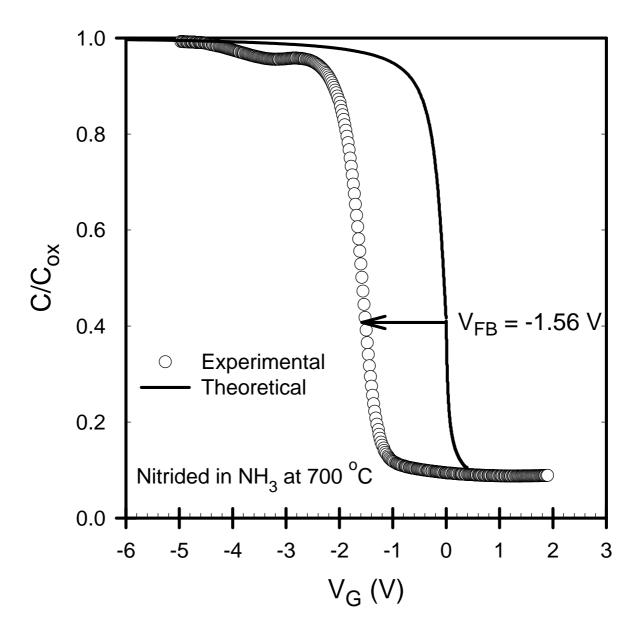

| Figure 4.24 | Theoretical and experimental high frequency normalized                                                                |    |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS            |    |

|             | capacitors prepared after nitridation process in NH <sub>3</sub> at 700°C7                                            | 5  |

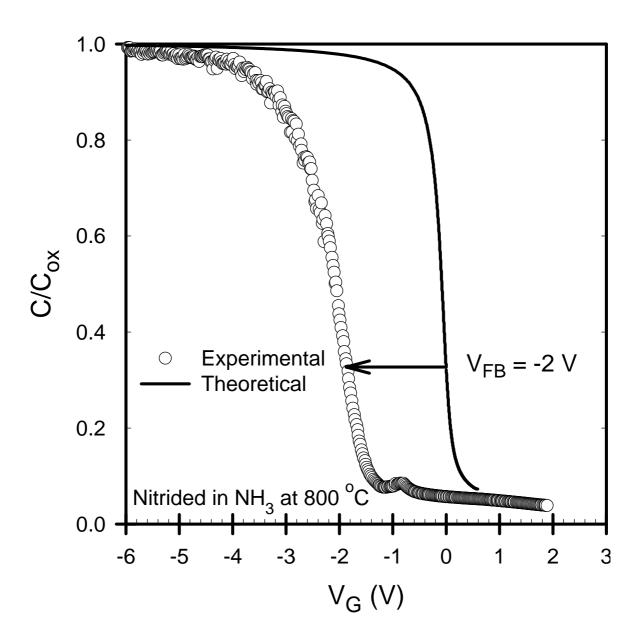

| Figure 4.25 | Theoretical and experimental high frequency normalized                                                                |    |

|             | capacitance-voltage curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS            |    |

|             | capacitors prepared after nitridation process in NH <sub>3</sub> at 800°C7                                            | 6  |

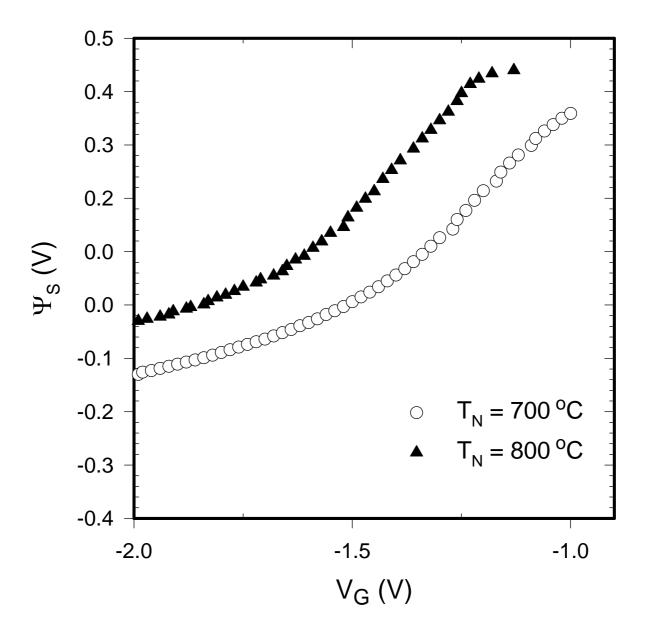

| Figure 4.26 | Surface potential $\psi_S$ versus gate voltage $V_G$ curves of Al-Ta <sub>2</sub> O <sub>5</sub> -                    |    |

|             | (SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared after a nitridation process in                          |    |

|             | NH <sub>3</sub> at 700°C and 800°C.                                                                                   | 8  |

| Figure 4.27 | Density of interface trap states as a function of energy in the band                                                  |    |

|             | gap of c-Si for Al-Ta $_2$ O $_5$ -(SiO $_x$ N $_y$ )-Si MOS capacitors prepared after                                |    |

|             | a nitridation process in $NH_3$ at $700^{\circ}C$ and $800^{\circ}C$ and with that of                                 |    |

|             | reference sample with native oxide SiO <sub>2</sub> 7                                                                 | '9 |

| Figure 4.28 | Comparison of high frequency capacitance versus gate voltage $V_{\text{G}}$                                           |    |

|             | curves of Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors prepared at         |    |

|             | nitridation temperature $T_N$ =800°C in NH <sub>3</sub> and N <sub>2</sub> O gas ambient8                             | 0  |

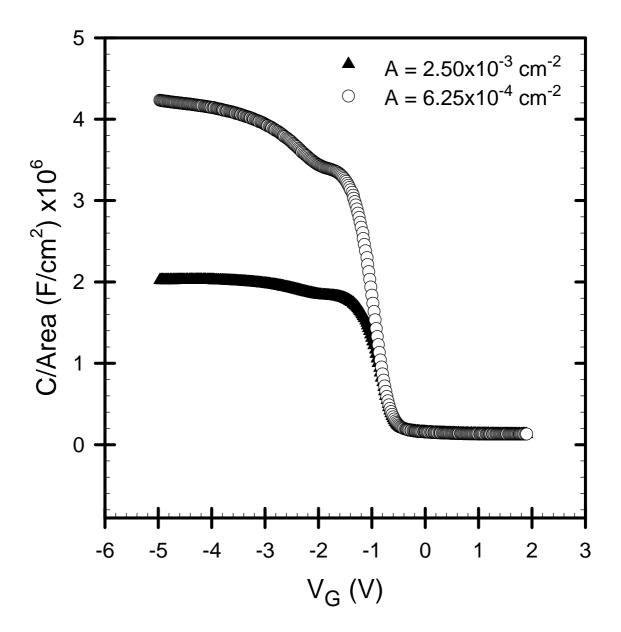

| Figure 4.29 | Comparison of experimental high frequency C-V curves of Al-                                                           |    |

|             | Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-Si MOS capacitors with two different gate area on  |    |

|             | the same substrate prepared after nitridation process in N <sub>2</sub> O gas at                                      |    |

|             | 800 C8                                                                                                                | 1  |

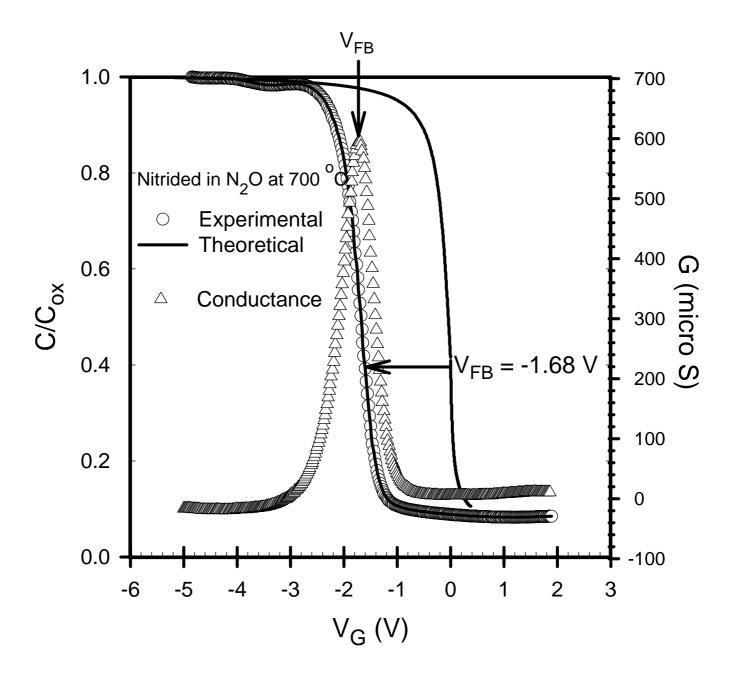

| Figure 4.30                  | Normalized Capacitance $C/C_{ox}$ versus gate voltage $V_G$ and               |    |  |  |  |  |

|------------------------------|-------------------------------------------------------------------------------|----|--|--|--|--|

|                              | conductance versus gate voltage V <sub>G</sub> graphs for the sample nitrided |    |  |  |  |  |

| in N <sub>2</sub> O at 700°C |                                                                               |    |  |  |  |  |

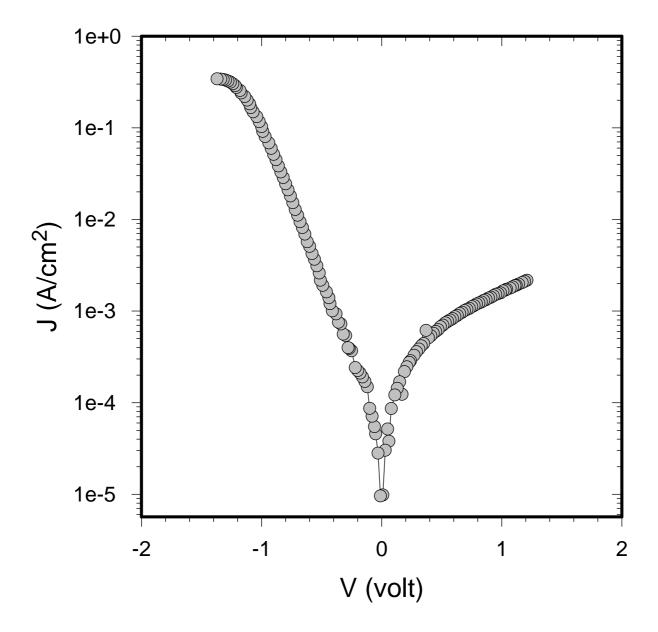

| Figure 4.31                  | Leakage current measurements of MOS devices.                                  | 84 |  |  |  |  |

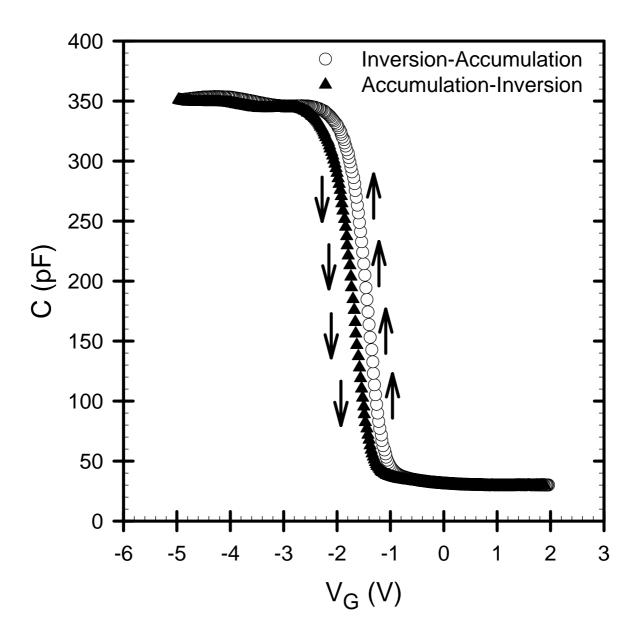

| Figure 4.32                  | Hysteresis curve of MOS device measured from accumulation to                  |    |  |  |  |  |

|                              | inversion and from inversion to accumulation                                  | 85 |  |  |  |  |

# LIST OF TABLES

| <u>Table</u> |                                                                                         | <b>Page</b> |

|--------------|-----------------------------------------------------------------------------------------|-------------|

| Table 2.1    | Deposition parameters of MOS structures used in this thesis                             | 12          |

| Table 4.1    | Summary of the parameters extracted from the high frequency C-V                         | r           |

|              | measurements for MOS capacitors with Ta <sub>2</sub> O <sub>5</sub> insulating layers.  | ,           |

|              | Data presented here are the average of six device characteristics                       | ;           |

|              | measured from different parts of the substrate wafer                                    | 53          |

| Table 4.2    | Summary of the parameters extracted from the high frequency C-V                         | r           |

|              | measurements for MOS capacitors with nitrided Ta <sub>2</sub> O <sub>5</sub> insulating | 5           |

|              | layers. Data presented here are the average of six device                               | <u>,</u>    |

|              | characteristics measured from different parts of the substrate wafer                    | 67          |

## **CHAPTER 1**

#### INTRODUCTION

In an article written in 1965, Gordon Moore described exponential growth in the number of transistors per integrated circuit and predicted this trend would continue. "Moore's Law" states that the number of transistors on integrated circuits doubles approximately every 24 months, resulting in higher performance at lower cost. This simple but profound statement is the foundation of semiconductor and computing industries. Similarly, to achieve 1 G-bit and higher capacity Dynamic Random Access Memories (DRAMs), the number of capacitors inside a chip must tremendously increase resulting in a miniaturization of device size which causes several different problems with the conventionally used gate insulators.

Native silicon dioxide (SiO<sub>2</sub>) is a high-quality electrical insulator and it is used as a barrier material for electrical isolation of semiconductor devices, as a component in Metal- Oxide-Semiconductor (MOS) capacitors of DRAMs. It has been studied in detail by many researchers since it was the only insulating material used for the production of integrated circuits (Nicollian and Brews 1982). The researchers have focused on depositing an electronic grade SiO<sub>2</sub> by using different methods to achieve the best quality electronic devices. Different pre- and post- deposition methods such as rapid thermal annealing (Paskaleva et al. 1995), and nitridation (Croci et al. 2001) were used to increase the electrical quality of SiO<sub>2</sub> insulating layers. Finally, the quality of these devices were examined by using different measurement methods such as Conductance Spectroscopy (Nicollian and Goetzberger 1965, Nicollian et al. 1969, Duval et al. 2001a, Duval et al. 2001b, Duval et al. 2003, De Dios et al. 1990), Capacitance -Voltage (C-V) Spectroscopy (Paskaleva et al. 2003, Paskaleva and Atanassova 2000b), Current-Voltage (I-V) measurements (Paskaleva and Atanassova 2000a) and noise measurements (Fleetwood 1992, Fleetwood et al. 1993).

Once the optimum deposition type and conditions are obtained, researchers have started to produce thinner and thinner layers of SiO<sub>2</sub> in order to increase the minimum cell capacitance. Even tough, the perfect conventional SiO<sub>2</sub>-Si structure is used in the production of 256 M-bit and lower capacity DRAMs, for the production of higher capacity DRAMs, the minimum cell capacitance must be studied in detail. Up to now, most of the strategies to satisfy the minimum cell capacitance have been focused

on an increase of the memory cell area as well as on decreasing of the dielectric thickness rather than using high dielectric constant materials. In practice, however, there is not much room for implementation of high capacitance by scaling down the dielectric thickness or expanding the capacitor area for gigabit scale DRAMs. From the thickness point of view, as CMOS devices are built with ever smaller features, the thickness of the conventional SiO<sub>2</sub> gate dielectric must be reduced. Finally, it has been realized that, after this long period of geometric scaling, it has been arrived at a point where the concomitant scaling of the thickness of the silicon dioxide (SiO<sub>2</sub>) gate dielectric has left it only a few nanometers thick, beyond which the material no longer possesses its inherent physical characteristics. As the thickness of silicon dioxide approaches less than 1.5 nm, the leakage current becomes higher than 1 A/cm<sup>2</sup> and tunneling current increases significantly so that increase in power dissipation and heat become critical issues. Although great success has been achieved, the current DRAM technology can not be extended to the gigabit scale and beyond because the thickness of the traditionally used native oxide SiO<sub>2</sub> has approached the physical limits of minimum thickness (~1.5 nm). Therefore, finding an alternative to SiO<sub>2</sub> is an enormous challenge for the materials, device and integration research community.

Since conventional gate oxide poses problems as device features are scaled down, it becomes necessary to develop new gate dielectric materials with properties similar to  $SiO_2$  and compatible with current complementary metal oxide semiconductor technology (Manchanda et al. 2001). These materials should meet the following fundamental and practical requirements:

- (a) dielectric constant higher than that of silicon dioxides (K=3.9),

- (b) thermodynamic stability on silicon,

- (c) amorphous after device integration,

- (d) low conduction for low leakage (tunneling current less than 10 mA/cm<sup>2</sup>) and low power consumption,

- (e) high carrier mobility at the dielectric/Si interface. Therefore, low interface state density ( $D_{it}$ ) ( $< 2 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ ),

- (f) high breakdown strength and acceptable reliability,

- (g) wide band gap,

- (h) negligible hysteresis in capacitance-voltage curves.

At this point, high dielectric constant insulating layers have become important to replace the native silicon dioxide used for the gate dielectric of DRAMS. The use of

high-k dielectrics will make it possible to achieve similar charge storage density as conventional dielectrics at relatively larger thicknesses. Many high dielectric constant materials have been reported that could potentially replace SiO<sub>2</sub>. These include SiO<sub>x</sub>N<sub>y</sub>, Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, CeO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, La<sub>2</sub>O<sub>3</sub>, SrTiO<sub>3</sub>, (Ba,Sr) TiO<sub>3</sub> and silicates of hafnium and zirconium which enable an increase of the packing density of devices without a further reduction of insulator thickness (Manchanda et al. 1998, Chin et al. 2000, Wilk et al. 2000, Albertin et al. 2003, Dwivedi et al. 1998, Han et al. 2003, Suvorova et al. 2003, Mikhelashvili and Eisenstein 2000, Atanassova 1999, Chaneliere et al. 1998 and references there in (7-14)). These materials exhibit the desired high dielectric constants for applications as gate dielectrics in sub 100 nm silicon technology. However, detailed studies need to be performed to evaluate the compatibility of these materials with the rest of the silicon integrated circuit manufacturing processes.

Among all the candidates,  $Ta_2O_5$  layers have received considerable attention because of their potential application as dielectric films for storage capacitors in high density DRAMs (Kim 2000) ,due to the relatively high dielectric constant (20-40) (depending on deposition conditions), high refractive index and adequate dielectric breakdown strength ( $\sim 10^6$  V/cm) (Dimitrova and Atanassova 1998a, Atanassova 1999). Historically,  $Ta_2O_5$  was first studied at 1970's because of its promising properties as an antireflective layer for optical or photovoltaic applications. In the following decades, studies have been focused on the ways of obtaining stable oxide layers and their potential applications. However, the real emergence of tantalum pentoxide as dielectric material happened during the last decade mainly because of an exceptional effort in the development of electronics devices using tantalum oxide films as dielectric layers (Chaneliere et al. 1998, Ezhilvalavan and Tseng 1999). Also, these studies have been motivated by the dramatic scaling down of silicon integrated circuits that has pushed conventional dielectric films close to their physical limit in terms of reduction of thickness and dielectric strength.

Tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>) has useful optical and dielectric properties. It is a fairly stable oxide with an orthorhombic or hexagonal structure, a melting point of 1870 °C and a density of 8.27 g cm<sup>-3</sup> (Pierson 1992). It is moderately hard with a Vickers hardness of 1400 kg mm<sup>-2</sup>. It has a refractive index of 2.1-2.2. It is an electrical insulator with a high dielectric constant (25-35). In addition, Ta<sub>2</sub>O<sub>5</sub> films find applications in various fields such as dielectric for storage capacitors, gate insulators in metal-oxide-semiconductor (MOS) devices, insulating layer in thin film electroluminescent devices,

sensitive layer in biological and chemical sensors, optical coatings, anti-reflection coatings and coatings for hot mirrors (Ezhilvalavan and Tseng 1999).

The properties of Ta<sub>2</sub>O<sub>5</sub> layers depend on stoichiometry, microstructure (grain size distribution), film thickness, characteristics of electrode and homogeneity of the film. Ta<sub>2</sub>O<sub>5</sub> film growth method significantly affects above parameters and consequently its dielectric properties. A variety of techniques such as RF magnetron sputtering, reactive sputtering, thermal oxidation, Chemical Vapour Deposition (CVD) (excimer laser assisted, low temperature, low pressure, photo, plasma, electron cyclotron resonance (ECR), Atmospheric Pressure, metal organic (MOCVD), Liquid source), vacuum evaporation, atomic layer deposition, sol-gel method and ion assisted deposition have been examined and used to deposit best quality Ta<sub>2</sub>O<sub>5</sub> insulating layers (Liu et al. 2004, Boughaba et al. 2000, Zhang et al. 1998, Four et al. 1999, Mooney at al. 1999, Boyd and Zhang 2000, Duenas at al. 2000, Atanassova and Spassov 1998, Atanassova and Spassov 2002, Atanassova 1999, Atanassova and Spassov 1998, Atanassova and Spassov 2002, Ezhilvalavan and Tseng 1999, Chaneliere et al. 1998, and references there in). Regardless of the method by which they are formed, however, the process must be economical and the resultant films must exhibit the following characteristics; good thickness uniformity, high purity and density, controlled composition stoichiometries, high degree of structural perfection, good electrical properties, excellent adhesion and good step converge.

After deposition, the physical, structural, optical, chemical and electrical properties of tantalum pentoxide films on silicon have been studied in detail (Chaneliere et al. 1998, Ezhilvalavan and Tseng 1999 and references there in). The characteristics of the insulating layers have been examined by using the methods; X-ray diffraction (XRD), X-ray photoelectron spectroscopy (XPS), Auger electron spectroscopy (AES), secondary ion mass spectrometry (SIMS), Fourier transform infrared (FTIR) absorbance, Capacitance-Voltage (C-V) Spectroscopy and Conductance Spectroscopy.

X-ray diffraction (XRD) and structural analyses show that, tantalum pentoxide has a crystalline or an amorphous structure depending on its deposition temperature. It is confirmed that the Ta<sub>2</sub>O<sub>5</sub> films annealed below 600 °C do not show any notable crystallization and the crystallization temperature of Ta<sub>2</sub>O<sub>5</sub> film grown by reactive sputtering lies between 650 °C and 700 °C (Kimura et al. 1983). The results were also consistent with other reports for anodically or thermally grown Ta<sub>2</sub>O<sub>5</sub> film (Harvey and Wilman 1961). More recently, another study reported similar crystallization behavior of

Ta<sub>2</sub>O<sub>5</sub> films deposited by LPCVD process (Chiu et al. 1997). It is therefore clear that the crystallization temperature of Ta<sub>2</sub>O<sub>5</sub> film does not depend on the method by which the film is grown. Crystalline tantalum pentoxide presents principally two phases; an orthorhombic phase and a hexagonal phase.

The optical properties such as the optical bandgap of tantalum pentoxide were determined by transmission and absorption spectroscopy (Burte and Raush 1995). From transmittance measurements, the bandgap value was found to be 5.28 eV for amorphous films. From absorbance measurements, values ranging from 4.2 to 4.4 eV for amorphous films and 3.9 to 4.5 eV for crystalline films were obtained. Tantalum pentoxide is transparent in the near UV spectral region ( $\lambda > 300$  nm), which is an important point for optoelectronic devices that operate in the ultraviolet, such as astronomical charge-coupled device (CCD) imagers and space based photovoltaic devices.

Electrical characterization results show that, the dielectric constant value obtained for tantalum pentoxide depends upon the sample characteristics and the experimental preparation method. It has also been demonstrated that the dielectric constant of Ta<sub>2</sub>O<sub>5</sub> layers shows thickness dependence, the dielectric constant decreases significantly with decreasing the Ta<sub>2</sub>O<sub>5</sub> layer thickness (Atanassova 1999). The dielectric permittivity of amorphous Ta<sub>2</sub>O<sub>5</sub> was found to be in the range 22-28 (Kukli et al. 1995, Devine et al. 1996). But values up to 40 have been reported for nonamorphous Ta<sub>2</sub>O<sub>5</sub> films (Nakagawa and Okada 1990). Recent studies have shown that the dielectric constant can be as high as ~60 for crystalline Ta<sub>2</sub>O<sub>5</sub> on Si (Chaneliere et al.). Crystalline Ta<sub>2</sub>O<sub>5</sub> exhibits a higher dielectric constant than amorphous Ta<sub>2</sub>O<sub>5</sub>. Moreover, the crystalline phases of tantalum pentoxide show an anisotropic character. Depending upon the crystal orientation, the dielectric constant could vary over a wide range, which would result in uncertainty in the capacitance per unit area if used to produce capacitors. The crystallographic orientation dependence of Si substrates on the dielectric constant of Ta<sub>2</sub>O<sub>5</sub> was reported by Seki et al. (Seki et al. 1984). They have noticed that for each substrate, the dielectric constant of deposited Ta<sub>2</sub>O<sub>5</sub> increases monotically with its thickness and there was a dependence of the dielectric constant on the substrate orientation. Therefore, an amorphous structure is needed for microelectronics applications, unless the crystal orientation can be controlled in order to obtain the same characteristics from one component to another.

As another issue, the effect of oxidation on the dielectric constant of the  $Ta_2O_5$  films was reported by some researchers (Atanassova et al. 2002a, Atanassova et al. 2002b, Park and Im et al. 1992). They showed that the dielectric constant obtained from an Al- $Ta_2O_5$ -Si capacitor depends on the thickness of the oxide and increases with increasing oxidation temperature.

Another important parameter that affects the dielectric constant of  $Ta_2O_5$  is the formation of an inevitable thin transition layer (in general  $SiO_2$ ). This thin oxide may drastically reduce the dielectric constant of the system since the dielectric constant of  $SiO_2$  is equal to 3.9, which is about 6 times lower than for amorphous  $Ta_2O_5$ . The global dielectric constant of the  $Ta_2O_5$ - $SiO_2$  system can be evaluated by using a simple model which supposes that the two dielectric layers are represented by two capacitors in series with the dielectric constant of silicon dioxide and tantalum pentoxide respectively. The effective dielectric constant of the sandwich ( $\epsilon_{eff}$ ) is then given by the following equation:

$$\varepsilon_{eff} = \frac{(d_s + d_t)\varepsilon_s\varepsilon_t}{d_t\varepsilon_s + d_s\varepsilon_t}$$

(1.1)

where  $d_s$  and  $d_t$  are the thicknesses of SiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> respectively, and  $\varepsilon_s$  and  $\varepsilon_t$  are the dielectric constants of SiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub> respectively. For example, if we consider 2 nm of SiO<sub>2</sub> and 15 nm of Ta<sub>2</sub>O<sub>5</sub>, the effective dielectric constant will be equal to 15.6, substantially lower than the ideal value of  $\varepsilon_t$  for pure amorphous Ta<sub>2</sub>O<sub>5</sub> ( $\varepsilon_t \sim 26$ ).

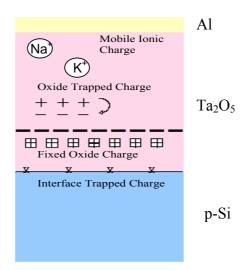

In addition, the non-ideal effects such as charges localized inside the oxide layer and at the silicon-insulator interface are of great importance. In the ideal metal-oxide-semiconductor (MOS) system, the oxide layer is assumed to be free of charges, and the insulator-semiconductor interface is assumed to be perfect. However, the deposition conditions, type and the environment causes non-ideal effects in the MOS structure by localizing charges inside the oxide layer or by creating interface trap states at the insulator-silicon interface. The electrically active defects localized in the insulator or at the insulator-semiconductor interface lead to the presence of the following different charges:

(a) oxide trapped charges which are due to electrons and holes trapped in the bulk of the insulator,

- (b) mobile ionic charges which are due to ionic impurities present in the bulk of the insulator,

- (c) fixed oxide charges which are due to structural defects localized in the insulator, near the insulator-semiconductor interface, and

- (d) interface trapped charges due to holes and electrons captured by trapping centers localized at the insulator-semiconductor interface.

The total of the oxide charges present in the oxide layer (the fixed oxide charges, mobile ionic charges and oxide trapped charges) is called as the effective oxide charge and it is represented by Qeff, and the density of interface trap states caused by the lattice mismatch problem between Ta<sub>2</sub>O<sub>5</sub> and silicon is represented by D<sub>it</sub>. The level of Q<sub>eff</sub> and Dit are determining the conduction mechanism through the oxide layer and are directly related with the quality of the device. For example, interface trap states captures charges from the silicon thus, lowering the total capacitance of the system. For this reason, it is crucial to evaluate the number of these charges and the resultant value must be kept as low as possible by optimizing the deposition conditions for the best device performance. There are many studies done for the determination of the level of these charges (Dimitrova and Atanassova 1998a, Dimitrova and Atanassova 1998b, Novkovski et al. 2005, Spassov et al. 2000, Atanassova et al. 2002a, Atanassova and Paskaleva 2002, Atanassova 1999, Ozdag et al. 2005). For the as-deposited samples values up to  $\sim 10^{12} \text{ eV}^{-1} \text{cm}^{-2}$  have been reported. However this level is quite high when compared with the level present in the conventional SiO<sub>2</sub>-Si system ( $\sim 10^{10}$  eV<sup>-1</sup>cm<sup>-2</sup>). For this reason, researchers are now focused on the pre- and post-deposition methods such as rapid thermal annealing or rapid thermal nitridation which can enable a decrease on the level of effective oxide charge and interface trap states as low as  $\sim 10^{11} \text{ eV}^{-1} \text{cm}^{-2}$ .

Concerning the leakage current density, common values are below 10<sup>-6</sup> and 10<sup>-7</sup> A/cm<sup>2</sup> under an applied electric field up to 3MVcm<sup>-1</sup> (Atanassova and Paskaleva 2003, Paskaleva et al. 2000, Chaneliere et al. 1998). However, these results greatly depend on the deposition methods and parameters like temperature, pressure etc., and on the preand post-deposition annealing treatments like annealing technique, gases employed, duration and temperature, presence of an interfacial layer and nature of this layer, which strongly influence the level of leakage current by playing an important role on the quality of the tantalum pentoxide layer. In addition, two main conduction mechanisms, Schottky emission and Poole-Frenkel effect were studied to explain the current transport

in tantalum pentoxide thin films (Atanassova and Paskaleva 2002, Chaneliere et al. 1998).

Chemical analyses result in that tantalum pentoxide is highly resistant to many chemicals depending upon its preparation technique and can in fact be employed as a protective coating material against corrosion.

Even tough so much work has been done on Ta<sub>2</sub>O<sub>5</sub>, its not completely understood yet. Although Ta<sub>2</sub>O<sub>5</sub> is now in the closest position to practical application, process optimization and detailed reliability data of this material need to be established before it can be confidently accepted into mass production and successfully integrated into full fabrication process of microelectronics devices.

## 1.1 Thesis objective

The objective of this thesis is to examine the electrical characteristics of Ta<sub>2</sub>O<sub>5</sub> insulating layers in detail because of its promising properties to replace the native silicon dioxide used for the gate dielectric of DRAMS. The most fundamental device structure for investigation of nearly all the electrical properties of a dielectric material is the metal-oxide-semiconductor (MOS) structure. In this thesis, Ta<sub>2</sub>O<sub>5</sub> insulating layer deposited under different preparation conditions on a p-type Silicon (Si) substrate are used to form metal-oxide-semiconductor (MOS) capacitors. Electrical properties of the MOS capacitors are studied in detail using capacitance-voltage (C-V) spectroscopy at 1 MHz. Conductance-voltage and current-voltage measurements were also performed to obtain additional information about the devices.

Using the theory of ideal MOS capacitors, theoretical capacitance-voltage characteristics have been calculated using a computer program. Experimental high frequency capacitance-voltage curve of each sample was compared with the ideal curve of the same sample. Dielectric constant of insulating layer, doping concentration of substrate, flat band voltages, maximum and minimum capacitance values, trapped oxide charges and interface trap density present at Si-Ta<sub>2</sub>O<sub>5</sub> interface have been derived from the ideal and experimental high frequency C-V curves. Detailed calculations proposed in the Terman's method were used to calculate the interface trap density present in the band gap of crystalline silicon. The results of MOS capacitors with different Ta<sub>2</sub>O<sub>5</sub>

insulating layers were compared with a reference sample, which has a native SiO<sub>2</sub> layer with a standard electronic property.

In order to understand the electronic quality of Ta<sub>2</sub>O<sub>5</sub> insulating layers deposited on Si substrate and interface quality of Si-Ta<sub>2</sub>O<sub>5</sub>, two different approaches have been carried out. First, Ta<sub>2</sub>O<sub>5</sub> insulating layers were directly deposited on the polished p-type substrate using the magnetron sputtering method with different thickness values. In the second approach, rapid thermal nitridation process under N<sub>2</sub>O and NH<sub>3</sub> gas environment has been carried out on the polished p-type silicon substrate. Then, 20 nm thick Ta<sub>2</sub>O<sub>5</sub> insulating layers were deposited on the nitrided surface of p-type silicon substrate. Finally, metal (Al) electrodes were evaporated to form the MOS capacitors. Eventually, devices were tested and detailed characterization of devices has been carried out using capacitance-voltage spectroscopy and results were compared with those obtained from the reference MOS capacitor with native oxide SiO<sub>2</sub>.

# **CHAPTER 2**

#### **EXPERIMENTAL**

## 2.1 Sample Preparation

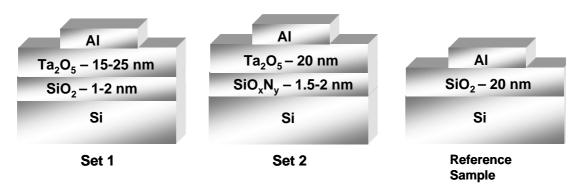

The samples that are used in this study are prepared in the form of Al-Ta<sub>2</sub>O<sub>5</sub>-Si MOS capacitors by using three different deposition methods for each layer present in the structure. The substrate is prepared by using Czochralski method, and then the oxide layer is formed by using the RF-magnetron sputtering method. Finally metal electrodes are formed by using thermal evaporation technique. The samples are deposited at Institute of Solid State Physics, Bulgarian Academy of Sciences, in Sofia, Bulgaria. The schematic view of three groups of samples that are used in this study can be seen in Figure 2.1.

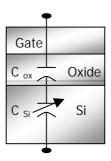

Figure 2.1 Schematic view of MOS structures that are used in this study

Czochralski method is a technique that is used in making single crystal silicon. A 2-3 mm diameter silicon seed crystal is rotated and lowered into a bath of molten Silicon (T> 1400 °C). Because of the temperature difference, some of the melt freezes onto the seed. Finally, the solid seed crystal is rotated and slowly extracted from the pool of molten Si. This method requires a careful control to give crystals desired purity and dimensions. The seed can be sliced into hundreds of smaller pieces that are called wafers and each wafer yields hundreds or thousands of integrated circuits. Depending on the purpose, silicon can be doped during the deposition. In this study, p type

crystalline Si that is formed by doping Si with Boron atoms is used as the substrate part of the MOS structure.

For sample Set 1, tantalum pentoxide films with thicknesses of 15-25 nm were deposited on p-type (100), 15  $\Omega$ cm Si, by RF magnetron sputtering from a tantalum target in an Ar atmosphere. The system base pressure was  $6x10^{-4}$  Pa, the working gas pressure 3 Pa, the RF power density 2.2 W/cm², the deposition rate, v = 9.3 nm/min, and the substrate temperature Ts = 300K. After the deposition, the Ta films were oxidized in dry oxygen at atmospheric pressure at 873 K with an  $O_2$  flow rate of 5.1 min<sup>-1</sup>. The thickness  $t_{ox}$  of the Ta<sub>2</sub>O<sub>5</sub> layers was measured by ellipsometry ( $\lambda = 632.8$  nm) and layers with  $t_{ox} = 15$ , 20 and 25 nm were investigated. For the electrical characterization, MOS capacitors were fabricated by evaporation of Al dots with a thickness of 500 nm, through a shadow mask with a gate electrode area of  $1.96x10^{-3}$  cm². For this group, post metallization annealing was carried out in H<sub>2</sub> at 723 K for 1h.

For sample Set 2, tantalum pentoxide layers of 20 nm were deposited on p-type (100), 3-5 $\Omega$ cm Si wafer by using RF magnetron sputtering in  $O_2$  gas environment. Before the deposition of  $Ta_2O_5$ , a rapid thermal nitridation (RTN) process is applied for 10 seconds in a clean room of class 10 in Germany by using  $N_2O$  and  $NH_3$  gases in the temperature range between 700-850 °C. After RTN, a silicon oxynitride layer of thickness ~1.5 nm was detected at the Si surface. The deposition of  $Ta_2O_5$  insulating layer is carried out by using RF-magnetron sputtering technique. However, in this case formation of  $Ta_2O_5$  is directly obtained during sputtering process with a Ta target in an oxygen rich environment. Hence, sputtered Ta atoms react with oxygen and form  $Ta_2O_5$  insulating layer on the substrate. The substrate temperature is held at 220 °C. Lastly, Al electrodes are evaporated with four different gate areas such as  $S_1$ = 2.5x10<sup>-3</sup> cm<sup>2</sup>,  $S_2$ = 6.25x10<sup>-4</sup> cm<sup>2</sup>,  $S_3$ = 2.25x10<sup>-4</sup> cm<sup>2</sup> and  $S_4$ = 1x10<sup>-4</sup> cm<sup>2</sup>, for the examination of the changes in the capacitance and the dielectric constant depending on the capacitor area.

Finally, a reference sample of Al-SiO<sub>2</sub>-Si is prepared by thermal oxidation of SiO<sub>2</sub> on p-silicon to compare electrical properties of high dielectric constant insulators with that of conventional oxides.

There are mainly two sets of  $Ta_2O_5$  MOS capacitors with or without nitridation process and a sample of  $SiO_2$  MOS capacitor as a reference conventional oxide that are used in this study. The detailed information about the process conditions of the samples are given in the Table 2.1.

Table 2.1 Deposition parameters of MOS structures used in this thesis

| Set 1- Rf Magnetron Sputtered Ta <sub>2</sub> O <sub>5</sub> Without Nitridation |                                                                               |                    |                        |    |                                         |  |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------|------------------------|----|-----------------------------------------|--|

| Sample Name                                                                      | Composition                                                                   | RTN                | RTN Process            |    | Area (cm <sup>2</sup> )                 |  |

| N 3                                                                              | Al- Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>2</sub> )-Si                    |                    | -                      | 15 | 1.96x10 <sup>-3</sup>                   |  |

| N 6                                                                              | Al- Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>2</sub> )-Si                    |                    | -                      | 20 | 1.96x10 <sup>-3</sup>                   |  |

| N11                                                                              | Al- Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>2</sub> )-Si                    |                    | -                      |    | 1.96x10 <sup>-3</sup>                   |  |

| S                                                                                | Set 2- Rf Magnetron Sputtered Ta <sub>2</sub> O <sub>5</sub> With Nitridation |                    |                        |    |                                         |  |

| Sample Name                                                                      | Composition                                                                   | RTN                | RTN Process            |    | Area (cm <sup>2</sup> )                 |  |

| RN 1                                                                             | Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-S       | i N <sub>2</sub> O | 700 °C                 | 20 | $2.5 \times 10^{-3} - 1 \times 10^{-4}$ |  |

| RN 2                                                                             | Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-S       | i N <sub>2</sub> O | 800 °C                 | 20 | $2.5 \times 10^{-3} - 1 \times 10^{-4}$ |  |

| RN 3                                                                             | Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-S       | i N <sub>2</sub> O | 850 °C                 | 20 | $2.5 \times 10^{-3} - 1 \times 10^{-4}$ |  |

| RN 4                                                                             | Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-S       | i NH <sub>3</sub>  | 700 °C                 | 20 | $2.5 \times 10^{-3} - 1 \times 10^{-4}$ |  |

| RN 5                                                                             | Al-Ta <sub>2</sub> O <sub>5</sub> -(SiO <sub>x</sub> N <sub>y</sub> )-S       | i NH <sub>3</sub>  | NH <sub>3</sub> 800 °C |    | $2.5 \times 10^{-3} - 1 \times 10^{-4}$ |  |

| Reference Sample – Thermal SiO <sub>2</sub>                                      |                                                                               |                    |                        |    |                                         |  |

| Sample Name                                                                      | Composition                                                                   | RTN Pro            | RTN Process            |    | Area (cm <sup>2</sup> )                 |  |

| SiO <sub>2</sub>                                                                 | Al-SiO <sub>2</sub> -Si                                                       | -                  |                        | 20 | 1.96x10 <sup>-3</sup>                   |  |

## 2.1 Characterization Techniques

In this section, the experimental method of Capacitance-Voltage Spectroscopy used for the electrical characterization of MOS devices will be explained in detail.

## 2.2.1 Capacitance Voltage (C-V) Spectroscopy

This method is a fast and accurate method in the determination of electronic quality of MOS devices. It is the first time that this experimental setup, Model 82-DOS Simultaneous C-V System, is established as one of the main goal of this thesis. The experimental setup is shown in Figure 2.2. Model 82-DOS is a computer controlled system of instruments designed to make simultaneous C-V, quasistatic C-V and high frequency (1 MHz) C-V measurements on MOS capacitors. The system includes a Keithley 590 C-V Analyzer for high frequency C-V measurements, and a Keithley 595 Quasistatic C-V Meter for low frequency C-V measurements. Additionally, Keithley 230 Programmable Voltage Source and Keithley 5951 Remote Input Coupler are used to apply voltage and control the communication between the instruments and the computer. A Keithley IEEE 488 Interface card is used to provide General Purpose Interface Bus (GPIB) communication between the instruments and the computer. Software package called Model 82-DOS is used for the control of the experimental setup, data collection and acquisition.

Figure 2.2 Simultaneous Capacitance-Voltage (C-V) Setup

After making necessary connections between the instruments and the computer by using the system block diagram provided in the users' manual, the software is installed by using the disks provided by Keithley. If the system is newly established or a new system configuration is present, there are some necessary steps that have to be done before beginning to the measurement. First of all, leakage current, stray capacitance detection and cable correction by using correction capacitors supplied by Keithley should be performed according to the steps explained in the manual. Later, the necessary modifications must be done on "Material.con" file for the constants defined for the sample studied, because the software is prepared for Al-SiO<sub>2</sub>-Si MOS structure. For example, the dielectric permittivity of Ta<sub>2</sub>O<sub>5</sub> is rewritten in the file for the place of dielectric permittivity of SiO<sub>2</sub> etc.

For the measurement, the sample is placed in a homemade sample box which is made up of aluminum metal to constitute a Faraday cage. It is important to place the sample in a Faraday Cage where the electric field vanishes inside, because of the sensitiveness of the measurement method which is based on the measurement of the charge or the capacitance versus applied voltage. In addition, the Faraday Cage must be lightproof, since the high quality MOS capacitors are excellent light detectors. The connections (gate and substrate) of the sample to the system are provided by using a homemade and designed probe station with micro manipulators to permit precise motion of the probe wire in two mutually perpendicular directions on the wafer. The probe wire used for the connection of gate is chosen to be gold to provide a good contact. The gold wire is sharpened by the process of electrolysis and sanding to be able to use it for smaller gate contact areas. This design with micro manipulators allows the measurement of different dots on the same wafer which is necessary for the reliable data collection. The contacts are placed on the sample under the optical microscope, which allows the choice of a good contact area. Finally, the sample holder is placed into the Faraday Cage for the measurement.

After placing the sample inside the Faraday Cage, the first step is to run a diagnostic C-V sweep to determine device parameters and to check to see that proper start and stop voltages have been programmed for the accumulation and inversion of the curve. The main menu of the software is shown in Figure 2.3.

By selecting option 3 in the main menu, it is possible to reach the sub menu for the diagnostic C-V measurement which is shown in Figure 2.4.

Keithley Capacitance Measurement System (c) copyright Keithley Instruments 1991 Version V2.0

-----

- \*\* MODEL 82 MAIN MENU \*\*

- 1. Reset Model 82 CV System

- 2. Test and Correct for System Leakages and Strays

- 3. Compensate for R<sub>series</sub> and Determine Device Parameters

- 4. Make CV Measurements

- 5. Analyze CV Data

- 6. Return to DOS

NOTE: ESC always returns user back one MENU level.

Figure 2.3 Model 82 Main Menu

\*\* Characterization of Device Parameters \*\*

#### OPEN CIRCUIT SUPPRESS SHOULD PRECEDE EACH MEASUREMENT

- 1. Set Measurement Parameters

- 2. Run Diagnostic CV Sweep

- 3. Graph Diagnostic Sweep Data to Determine INVERSION & ACCUMULATION Voltages.

- 4. ACCUMULATION: Determine Rseries, Cox, Tox, and/or Area.

- 5. INVERSION: Determine Cmin and Equilibrium Delay Time.

- 6. Return to Main Menu

Figure 2.4 Characterization of device Parameters Menu

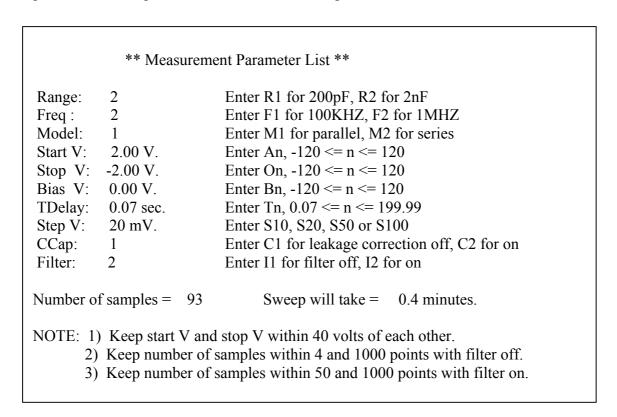

Before starting the measurement, the most important thing is to set measurement parameters, such as start and stop voltages, delay time, step voltage etc. by selecting option 1 in Figure 2.4. Measurement parameter list is shown in Figure 2.5.

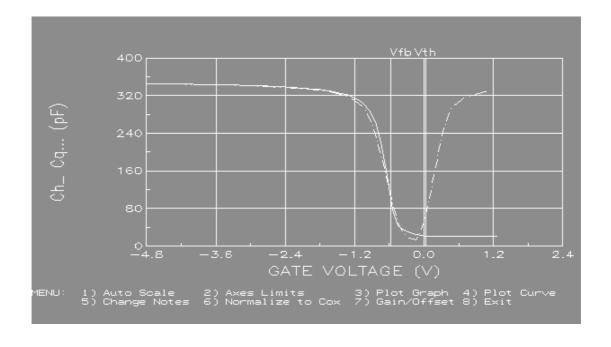

After setting the measurement parameters, it is possible to start the diagnostic C-V sweep. At the end of the sweep, a graph of capacitance versus voltage is plotted. A typical C-V graph can be seen in Figure 2.6. If the sample shows desired capacitance voltage characteristics, then by biasing the sample into accumulation and inversion, important device parameters such as series resistance, oxide capacitance, area or

thickness, minimum capacitance and optimum delay time can be determined using options 4 and 5 in parameters menu shown in Figure 2.4.

Figure 2.5 Measurement parameter List Menu

Figure 2.6 High and Low frequency C-V graphics of a MOS device.

Once the optimum device parameters are obtained, it is possible to run a real C-V sweep by selecting option 4 in Figure 2.3. In this case the sub menu for the C-V measurement is shown in Figure 2.7. By selecting option 2 in Figure 2.7, a C-V sweep can be started manually.

\*\* Device Measurement and Analysis \*\*

#### OPEN CIRCUIT SUPPRESS SHOULD PRECEDE EACH MEASUREMENT

- 1. Set Measurement Parameters

- 2. Manual Start CV Sweep

- 3. Auto Start CV Sweep

- 4. Analyze Sweep Data

- 5. Return to Main Menu

Figure 2.7 Device Measurement and Analysis Menu.

Before starting the measurement, again measurement parameters can be redefined depending on the purpose. For example, step voltage can be chosen as small as possible (10 mV) in order for the program to take as many data points as possible for the reliability of the analysis. At the end of the sweep, option 4 in Figure 2.7 can be chosen for the analysis of the sweep data. The graphs that the software can plot are seen in Figure 2.8 and the analyses are explained in detail in the users' manual.

By using menu in Figure 2.8, the data array can be saved to a file and the graphs can be plotted. However, there is an important point to be careful about the analysis. The software uses both high and low frequency C-V results for the determination of some parameters such as density of Interface trap states (D<sub>it</sub>). Nevertheless, low frequency C-V measurements of high dielectric constant insulators are a rather difficult task. It should be noted that low frequency C-V characteristics obtained by the ramp voltage or the feedback charge-voltage method have not been successfully investigated for Ta<sub>2</sub>O<sub>5</sub> capacitors. This can be explained by the fact that the leakage current is higher than the displacement current for most gate voltages. For this reason, by using the data file obtained at the end of the C-V measurement and by using Terman's method defined for MOS devices, interface trap density value can be analyzed manually. The detailed information about the analysis and the physics of MOS devices will be explained in the next chapter.

#### \*\* SWEEP DATA ANALYSIS \*\*

- 1. Save Measurement Data Array to File

- 2. Load Measurement Data Array from File

- 3. Display Data Arrays

- 4. Display Analysis Constants

- 5. Graph Quasistatic C vs. Gate Voltage

- 6. Graph High Frequency C vs. Gate Voltage

- 7. Graph Both Cq and Ch vs. Gate Voltage

- 8. Graph Q/t Current vs. Gate Voltage

- 9. Graph Conductance vs. Gate Voltage

- 10. Graph Doping Profile vs. Depth

- 11. Graph Ziegler Doping Profile vs. Depth

- 12. Graph Depth vs. Gate Voltage

- 13. Graph 1/Ch^2 vs. Gate Voltage

- 14. Graph Dit vs. Energy

- 15. Graph Band Bending vs. Gate Voltage

- 16. Graph Quasistatic C vs. Band Bending

- 17. Graph High Frequency C vs. Band Bending

- 18. Return to Previous Menu

Enter number to select from menu:

Figure 2.8 Sweep Data Analysis Menu.

The dielectric constant, doping concentration and flat band voltage values were determined from the experimental high frequency C-V curves. Theoretical ideal C-V characteristics were calculated using a computer program and equations defined for MOS devices. The effective oxide charge density, Neff, and the density of interface defect states, Dit, were calculated from the high frequency C-V curves using Terman's method.

#### **CHAPTER 3**

#### PHYSICS OF MOS DEVICES AND ANALYSIS

## 3.1 Ideal Metal-Oxide-Semiconductor (MOS) Energy Band Diagrams

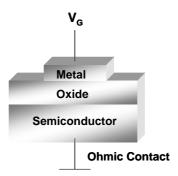

Metal-oxide-semiconductor (MOS) capacitor is one of the important solid state devices. It is constructed using a p-type or n-type single crystalline semiconductor wafer as substrate. An oxide layer is formed using different deposition methods and finally metal electrode is evaporated on top of the device, which is also called gate electrode. Other end of the substrate has an ohmic contact. In general, a silicon wafer is used for the substrate and native oxide SiO<sub>2</sub> is formed by using dry or wet oxidation process. Finally, aluminum gate electrode is evaporated to complete device fabrication. Cross-section of Metal-Oxide-Semiconductor structure is shown in Figure 3.1, where V<sub>G</sub> is the applied gate voltage. For the ideal MOS capacitor, both the oxide and the oxide-semiconductor interface are assumed to be free of charges and defect states. Depending on the polarity and magnitude of the applied gate voltage, the carrier concentration and band structure of semiconductor changes resulting in different electrical characteristics of the MOS capacitor. In general MOS capacitor operates at three different bias conditions.

Figure 3.1 Ideal MOS Structure with applied gate voltage V<sub>G</sub>

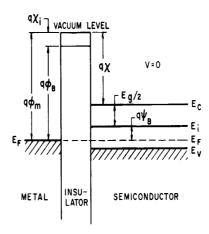

When  $V_G = 0$ , the structure is in thermal equilibrium. At this condition, the energy band diagram of a MOS structure with a p-type substrate is shown in Figure 3.2, where  $\phi_m$  is

the metal work function,  $\chi_i$  is the electron affinity of insulator,  $\chi$  is the electron affinity of semiconductor,  $E_g$  is the energy gap of semiconductor,  $\phi_B$  is the potential difference between the metal Fermi level and conduction band of the insulator,  $\psi_B$  is the potential difference between the intrinsic Fermi level ( $E_i$ ) and Fermi level ( $E_F$ ) inside the bulk,  $E_C$  is the conduction band and  $E_V$  is the valance band of the semiconductor. The importance of these energy barriers is that they prevent the free flow of carriers from the metal to the silicon or vice versa. Thus the application of a bias across the MOS capacitor does not result in current flow. Rather, an electric field is established in the oxide by surface charge layers that form in the metal and on the silicon-oxide interface.

Figure 3.2 Energy-Band diagram of ideal MOS structure in thermal equilibrium constructed from a p-type semiconductor substrate

Depending on the parameters defined above, an ideal MOS structure can be explained as follows:

(a) When the applied gate voltage  $V_G = 0$ , then the work function difference  $\phi_{ms}$ , between the semiconductor  $\phi_s$  and the metal  $\phi_m$  becomes zero, which means the energy bands are flat. Then from Figure 3.2, the work function difference can be written as follows:

$$\phi_{ms} = \phi_m - \phi_s = \phi_m - (\chi + \frac{E_g}{2q} + \psi_B) = 0$$

(3.1)

- (b) When a gate voltage  $V_G \neq 0$  is applied to an ideal MOS structure, the charges are distributed at the semiconductor-insulator or metal-insulator interface with equal amount and opposite polarities,

- (c) It is assumed that under applied gate voltage  $V_G$ , there is no charge transfer throughout the insulator, which means that it has an infinite resistance.

When a positive or negative gate voltage is applied to an ideal MOS structure, there are mainly three working conditions present in the semiconductor:

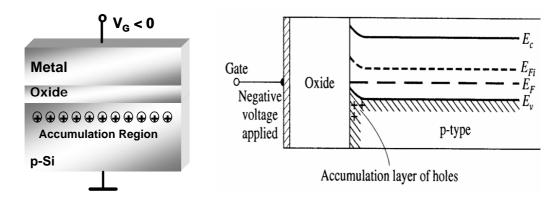

(1) Accumulation: When a negative voltage  $V_G$  is applied to metal terminal of MOS structure, the metal part becomes negatively charged and the semiconductor part becomes positively charged, then there occurs an internal electric field in the direction of upwards from semiconductor to metal. This electric field piles up holes of p-type semiconductor to the semiconductor-oxide interface, where an accumulation region of holes is obtained. The change in the free carrier concentration at the interface also changes the band diagram of semiconductor at the interface as shown in Figure 3.3. Free electron, n, and hole, p, concentrations of semiconductor at the oxide-semiconductor interface are explained as:

$$p = N_V \exp[-(E_F - E_V)/kT]$$

$$n = N_C \exp[-(E_C - E_F)/kT]$$

(3.2)

where  $E_F$  is the Fermi level energy,  $E_V$  is the valance band energy and  $E_C$  is the conduction band energy. As the hole concentration (p) increases at the interface,  $E_F$ - $E_V$  term must decrease. Therefore, the valance band, conduction band and intrinsic Fermi level bends up at the interface. The resulting band diagram and MOS structure in accumulation are shown in Figure 3.3. Then, MOS capacitor in this condition behaves like a parallel plate capacitor and system capacitance becomes equal to that of oxide capacitance,  $C_{ox}$ .

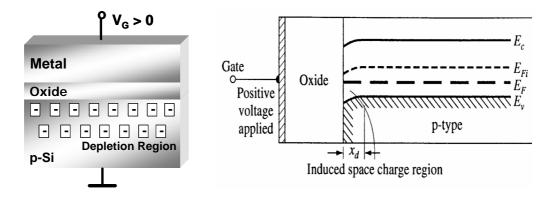

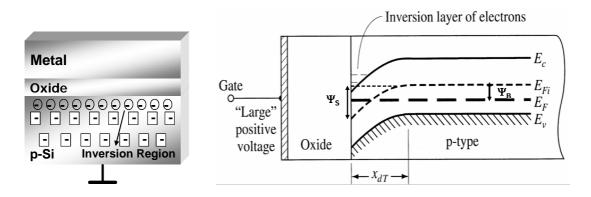

(2) Depletion: When a positive voltage  $V_G$  is applied to metal terminal of MOS structure, the metal part becomes positively charged and the semiconductor part becomes negatively charged. Then, there occurs an internal electric field in the direction of downwards from metal to semiconductor. Under the influence of the electric field holes at the interface of semiconductor are pushed towards the bulk silicon. At the oxide-semiconductor interface, majority carrier hole density decreases. This surface region is called "depletion region" or "space charge region". Only ionized acceptor atoms fixed to the silicon network remain in the depletion region. They are negatively

charged. Similarly from Equation 3.2, the decrease of hole concentration at the interface causes an increase in  $(E_F-E_V)$ , which results in the bands to bend down at the semiconductor-oxide interface. At this condition, cross section and energy band diagram of MOS capacitor are exhibited on Figure 3.4.

Figure 3.3 Cross-section and energy band diagram of MOS capacitor in accumulation region

Figure 3.4 Cross-section and energy band diagram of MOS capacitor in depletion region